# Distributed Real-time Architecture for Mixed Criticality Systems

## Description of Development Process with Model Transformations D 1.3.1

| Project Acronym     | DREAMS        | Grant Agreement<br>Number |  | FP7-ICT-2013.3.4-61 | 0640  |

|---------------------|---------------|---------------------------|--|---------------------|-------|

| Document<br>Version | 1.0           | <b>Date</b> 2014-07-31    |  | Deliverable No.     | 1.3.1 |

| Contact Person      | Leire Rubio   | Organisation              |  | IK4-IKERLAN         |       |

| Phone               | +34-943712400 | E-Mail                    |  | lrubio@ikerlan.es   |       |

## Contributors

| Name                                 | Partner     |

|--------------------------------------|-------------|

| Leire Rubio, Asier Larrucea          | IKL         |

| Gebhard Bouwer, Gernot Klaes         | TÜV         |

| Simon Barner, Alexander Diewald      | FORTISS     |

| José Enrique Simo Ten, Alfons Crespo | UPV/FENTISS |

| Thomas Koller, Obaid Ur-Rehman       | USIEGEN     |

| Jörn Migge                           | RTaW        |

| Arjan Geven                          | TTT         |

| Anton-Aart Trapman                   | ALSTOM      |

# Table of Contents

| С  | ontribut | tors   |                                                              | 2  |

|----|----------|--------|--------------------------------------------------------------|----|

| Ta | ble of ( | Conte  | ents                                                         | 3  |

| Fi | gure Ind | dex    |                                                              | 5  |

| Τa | ble Ind  | ex     |                                                              | 6  |

| G  | ossary.  |        |                                                              | 7  |

| 1  | Intro    | oduct  | ion                                                          | 9  |

|    | 1.1      | Cont   | text                                                         | 9  |

|    | 1.2      | Obje   | ectives of the document                                      | 9  |

|    | 1.3      | Stru   | cture of the document                                        | 9  |

|    | 1.4      | IEC 6  | 51508 Safety Life Cycle Overview                             | 9  |

| 2  | Defi     | nitior | n of DREAMS Development Process                              | 13 |

|    | 2.1      | Safe   | ty Approach                                                  | 13 |

|    | 2.1.3    | 1      | Impact of DREAMS characteristics on the development process  | 14 |

|    | 2.1.2    | 2      | DREAMS Safety Life-Cycle Specification                       | 22 |

|    | 2.1.3    | 3      | Measures for fault avoidance within DREAMS                   | 22 |

|    | 2.2      | Secu   | ırity Approach                                               | 24 |

|    | 2.2.2    | 1      | Impact of security aspects on the DREAMS development process | 24 |

|    | 2.2.2    | 2      | DREAMS Security Lifecycle Specification                      | 28 |

|    | 2.2.3    | 3      | Measures for fault avoidance within DREAMS                   | 32 |

|    | 2.3      | Timi   | ng Approach                                                  | 32 |

|    | 2.3.2    | 1      | GMP                                                          | 32 |

|    | 2.3.2    | 2      | Impact of DREAMS characteristics on the development process  | 35 |

|    | 2.3.3    | 3      | DREAMS Timing Lifecycle Specification                        | 37 |

|    | 2.4      | Sum    | mary of DREAMS Development Process                           | 39 |

| 3  | DRE      | AMS    | Meta-Models and Model-Transformations                        | 41 |

|    | 3.1      | Impa   | act of DREAMS Characteristics                                | 41 |

|    | 3.2      | Intro  | oduction                                                     | 43 |

|    | 3.2.2    | 1      | (Meta-)Modelling                                             | 43 |

|    | 3.2.2    | 2      | MDE tool-chain                                               | 45 |

|    | 3.2.3    | 3      | DREAMS System Model                                          | 47 |

|    | 3.3      | Auto   | oFocus3 Meta-Model                                           | 49 |

|    | 3.3.2    | 1      | Requirements perspective                                     | 50 |

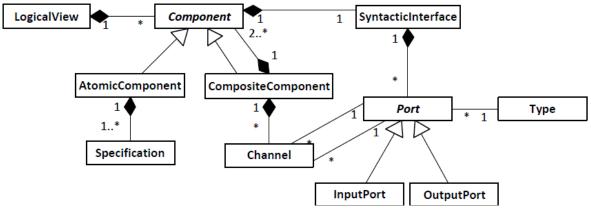

|    | 3.3.2    | 2      | Logical Perspective                                          | 51 |

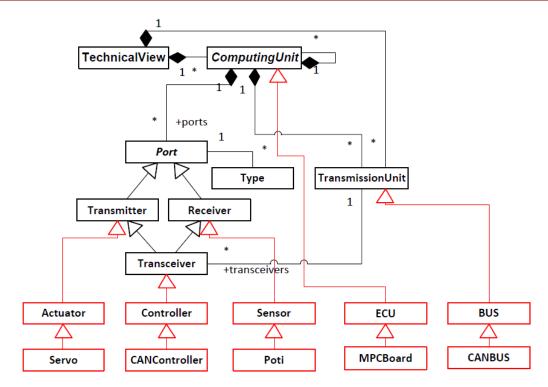

|    | 3.3.3    | 3      | Technical Perspective                                        | 54 |

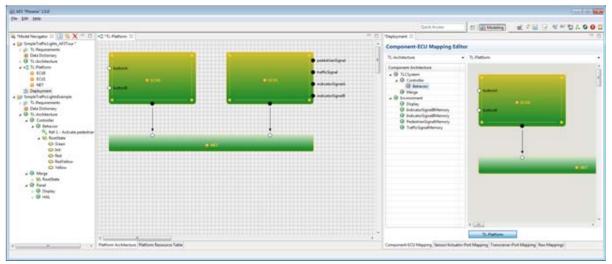

|    | 3.3.4    | 4      | Deployment Perspective                                       | 56 |

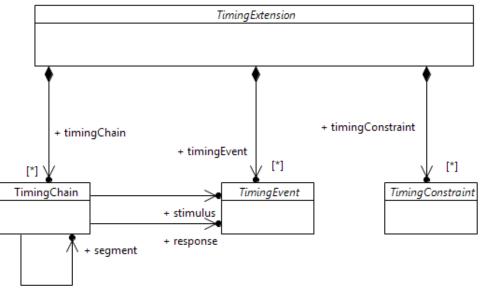

|    | 3.4      | Timi   | ng requirements Meta-Model                                   | 56 |

|    | 3.5      | Mult   | tiPARTES Meta-Model                                          | 61 |

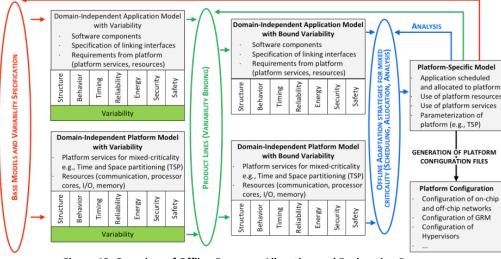

|     | 3.5.1     | Overview: Meta-Models, Toolset and Transformations        | 61 |

|-----|-----------|-----------------------------------------------------------|----|

|     | 3.5.2     | Safety Consistency Model                                  | 64 |

|     | 3.5.3     | Safety Compliance Model                                   | 64 |

|     | 3.5.4     | Diagnostics Techniques and Measure Model                  | 65 |

|     | 3.5.5     | Safety Integrity Levels Model                             | 66 |

| 3   | .6 Moo    | del-to-model Transformations                              | 66 |

|     | 3.6.1     | Generic DREAMS Development Process                        | 66 |

|     | 3.6.2     | Exemplary Development Process using Concrete Technologies | 73 |

| 4   | Requiren  | nents Matrix                                              | 79 |

| 5   | Bibliogra | phy                                                       | 83 |

| Ter | minology. |                                                           | 84 |

# **Figure Index**

| FIGURE 1: OVERALL SAFETY LIFE CYCLE                                                                          |      |

|--------------------------------------------------------------------------------------------------------------|------|

| FIGURE 2: E/E/PE SAFETY LIFE CYCLE                                                                           |      |

| Figure 3: Software Safety Life Cycle                                                                         |      |

| FIGURE 4: SOFTWARE DEVELOPMENT PROCESS (V-MODEL)                                                             | . 12 |

| Figure 5: Hardware Development Process (V-model)                                                             | . 12 |

| FIGURE 6: ASIC DEVELOPMENT SAFETY LIFE CYCLE (V-MODEL).                                                      | .13  |

| FIGURE 7: SYSTEM DEVELOPMENT SAFETY LIFECYCLE (THE V-MODEL)                                                  | . 14 |

| FIGURE 8: MEET-IN-THE-MIDDLE DESIGN FLOW OF DREAMS                                                           |      |

| Figure 9: Modular design of DREAMS                                                                           |      |

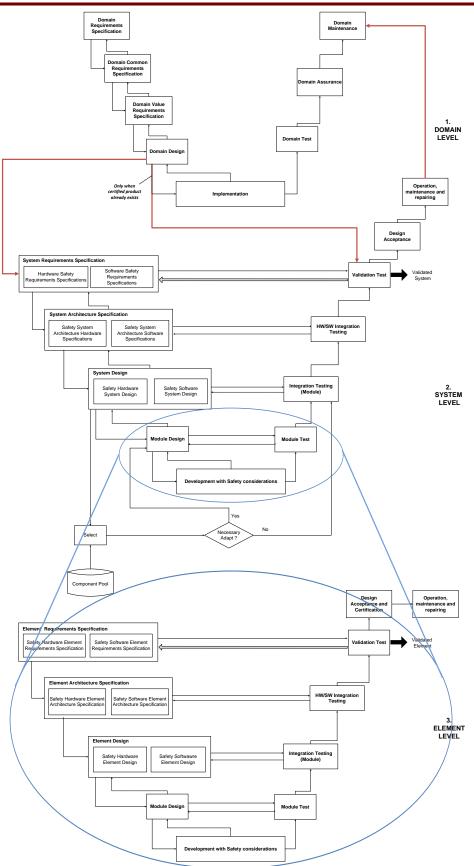

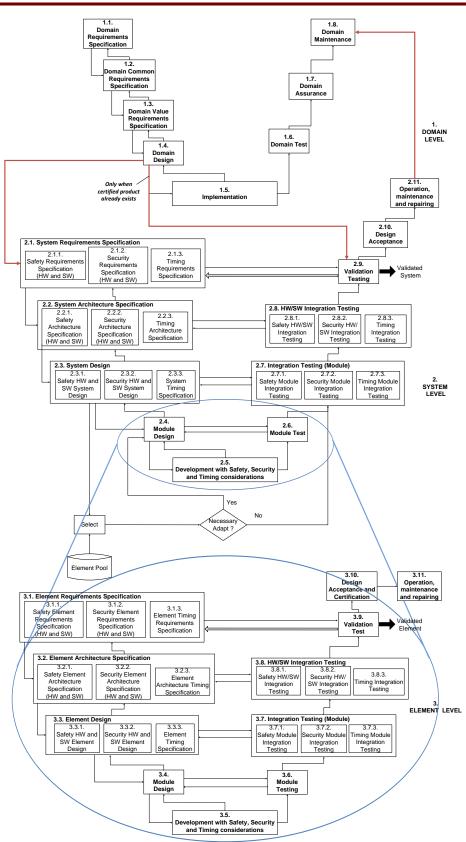

| FIGURE 10: DREAMS SYSTEM AND ELEMENT DEVELOPMENT PROCESSES.                                                  |      |

| FIGURE 11: COMPONENT BASED DREAMS DEVELOPMENT PROCESS.                                                       | . 20 |

| Figure 12: Domain Engineering and Product Engineering                                                        |      |

| Figure 13: Safety-related Development Process of DREAMS.                                                     |      |

| FIGURE 14: SECURITY REQUIREMENTS IN THE MEET-IN-THE-MIDDLE DESIGN FLOW OF DREAMS                             |      |

| FIGURE 15: SECURITY REQUIREMENTS AND THREAT MODEL FOR DREAMS                                                 |      |

| Figure 16: Modular design of DREAMS                                                                          |      |

| FIGURE 10. MODULAR DESIGN OF DREAMIS                                                                         |      |

|                                                                                                              |      |

| FIGURE 18: TRUSTWORTHY SECURITY DEVELOPMENT LIFECYCLE (SDL) PROPOSED BY MICROSOFT                            |      |

| FIGURE 19: SECURITY DEVELOPMENT LIFECYCLE BASED ON ISO/IEC 21827                                             |      |

| FIGURE 20: SECURITY DEVELOPMENT PROCESS OF DREAMS                                                            |      |

| FIGURE 21: GMP FOR TIMING                                                                                    |      |

| FIGURE 22: ABSTRACTING TIMING PROPERTIES (TIMMO-2-USE)                                                       |      |

| FIGURE 23: TIMING-RELATED DEVELOPMENT PROCESS                                                                |      |

| FIGURE 24: DREAMS DEVELOPMENT PROCESS                                                                        |      |

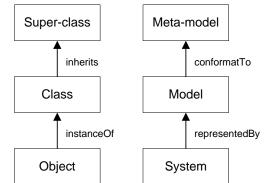

| FIGURE 25: COMPARISON OF OBJECT TECHNOLOGY AND MODEL-DRIVEN ENGINEERING (MDE)                                | .44  |

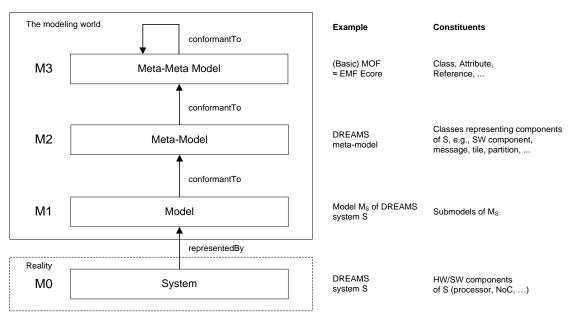

| FIGURE 26: 4-LEVEL MODEL ARCHITECTURE                                                                        | . 45 |

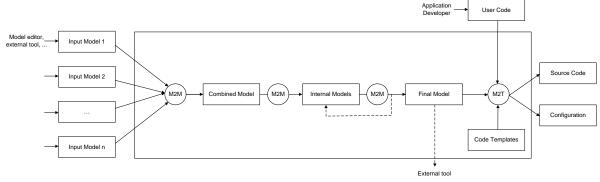

| FIGURE 27: GENERAL ARCHITECTURE OF MDE TOOL-CHAIN.                                                           | .46  |

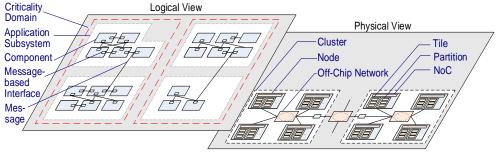

| FIGURE 28: SYSTEM STRUCTURE OF APPLICATION (LOGICAL VIEW) AND STRUCTURE OF PLATFORM (PHYSICAL VIEW) [D1.2.1] | .47  |

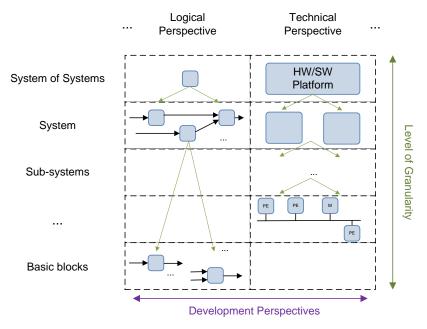

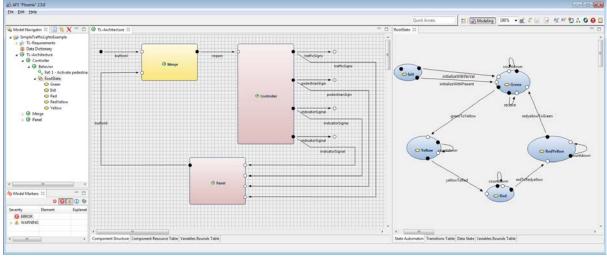

| FIGURE 29: DIMENSIONS OF ABSTRACTION: GRANULARITY LEVELS, AND DEVELOPMENT PERSPECTIVES                       | . 49 |

| FIGURE 30: AUTOFOCUS3 REQUIREMENTS PERSPECTIVE                                                               | .51  |

| FIGURE 31: AUTOFOCUS3 LOGICAL PERSPECTIVE                                                                    | . 52 |

| FIGURE 32: META-MODEL OF LOGICAL PERSPECTIVE                                                                 | . 52 |

| FIGURE 33: AUTOFOCUS3 TECHNICAL PERSPECTIVE AND DEPLOYMENT PERSPECTIVE                                       |      |

| FIGURE 34: META-MODEL OF TECHNICAL PERSPECTIVE                                                               |      |

| Figure 35: Timing Extension                                                                                  |      |

| Figure 36: Timing Constrains                                                                                 |      |

|                                                                                                              |      |

| FIGURE 37 : MIDDULAR STNCHRONIZATION CONSTRAINTS                                                             |      |

| FIGURE 39: DREAMS TIMING EXTENSIONS                                                                          |      |

|                                                                                                              |      |

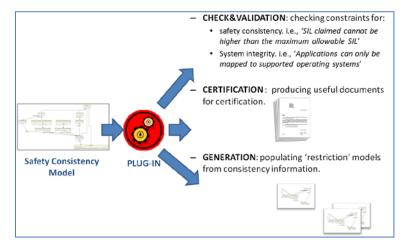

| FIGURE 40: SAFETY CONSISTENCY CHECK, USEFUL DOCUMENTS FOR CERTIFICATION AND GENERATION OF RESTRICTIONS.      |      |

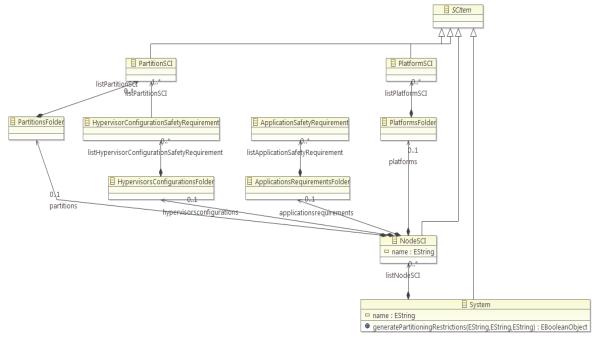

| FIGURE 41: SAFETY CONSISTENCY MODEL                                                                          |      |

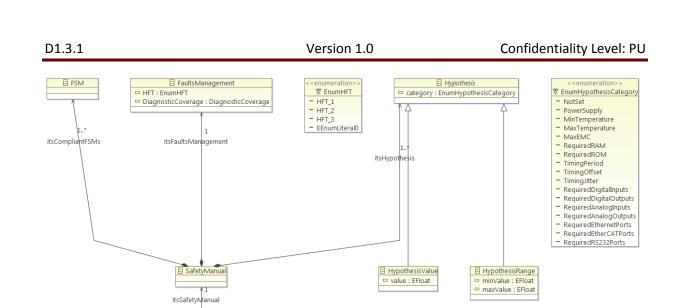

| FIGURE 42: SAFETY COMPLIANT ITEM AND SAFETY MANUAL MODELS                                                    |      |

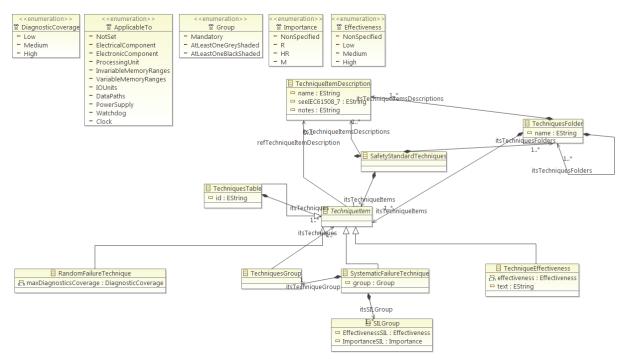

| FIGURE 43: DIAGNOSTIC TECHNIQUES AND MEASURE MODEL.                                                          |      |

| FIGURE 44: INSTANCE OF THE DIAGNOSTIC TECHNIQUES AND MEASURE MODEL FOR IEC-61508.                            |      |

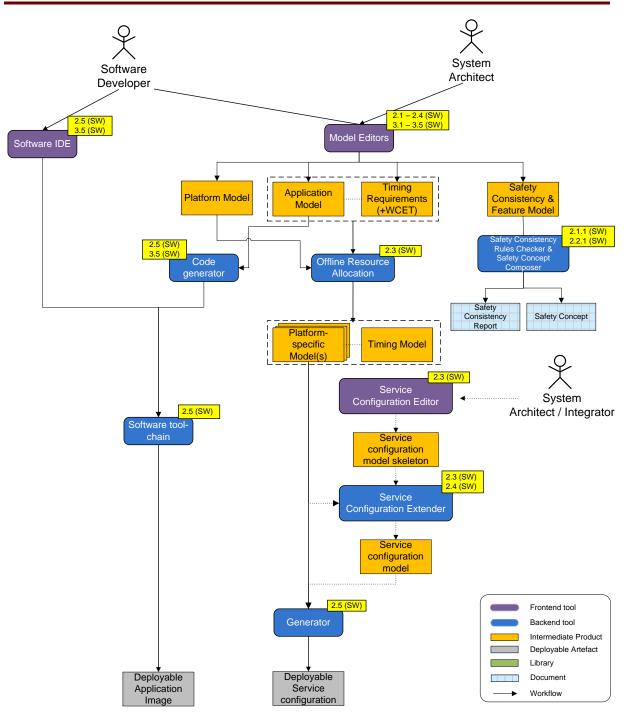

| FIGURE 45: OVERVIEW OF DREAMS SOFTWARE DEVELOPMENT & DEPLOYMENT WORKFLOW                                     |      |

| FIGURE 46: CHECKING PROCESS AND DIAGNOSTIC TECHNIQUES INFORMATION PANEL.                                     |      |

| FIGURE 47: EXAMPLE OF WIND POWER CERTIFICATION DOCUMENT                                                      |      |

| FIGURE 48: OVERVIEW OF OFFLINE RESOURCE ALLOCATION AND EXPLORATION PROCESS                                   |      |

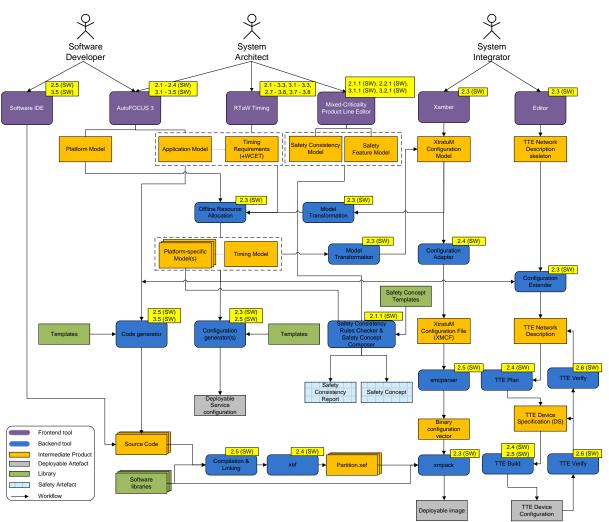

| FIGURE 49: DREAMS SOFTWARE DEVELOPMENT WORKFLOW: TOOLS, TRANSFORMATIONS AND IMPLEMENTATION ARTEFACTS         | .74  |

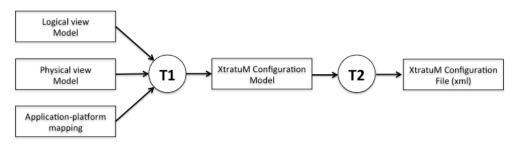

| FIGURE 50: CONTEXT OF XTRATUM CONFIGURATION MODEL                                                            | .76  |

| FIGURE 51: PARTS OF XTRATUM CONFIGURATION MODEL.                                                             | . 77 |

|                                                                                                              |      |

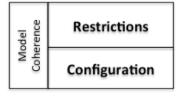

| Figure 52: TTE tool-chain workflow                                                                           | . 78 |

| FIGURE 52: TTE TOOL-CHAIN WORKFLOW<br>FIGURE 53: TTE TOOL-CHAIN DATAFLOW                                     |      |

## **Table Index**

| TABLE 1: ANALYSIS OF DREAMS REQUIREMENTS                                 | 15 |

|--------------------------------------------------------------------------|----|

|                                                                          |    |

| TABLE 2: TRACEABILITY OF DREAMS DEVELOPMENT PROCESS.                     | 18 |

| TABLE 3: IMPACT OF SECURITY ASPECTS INTO THE DREAMS DEVELOPMENT PROCESS. | 25 |

| TABLE 4: ANALYSIS OF DREAMS TIMING REQUIREMENTS                          | 35 |

| TABLE 5: IMPACT OF DREAMS CHARACTERISTICS ONTO META-MODELS               | 42 |

| TABLE 6: IMPACT OF DREAMS CHARACTERISTICS ONTO MODEL-TRANSFORMATIONS     | 43 |

| TABLE 7: DREAMS REQUIREMENT MATRIX.                                      | 82 |

|                                                                          |    |

## Glossary

| ΑΡΙ         | Application Programming Interface                                    |

|-------------|----------------------------------------------------------------------|

| ASIC        | Application Specific Integrated Circuit                              |

| ASIL        | Automotive Safety Integrity Level                                    |

| ATL         | Atlas Transformation Language                                        |

| CMOF        | Complete MOF                                                         |

| CPLD        | Complex Programmable Logic Device                                    |

| DREAMS      | Distributed Real-Time Architecture for Mixed Criticality Systems     |

| E /E /PE    | Electrical/Electronic/Programmable Electronic                        |

| EAST-ADL    | EAST Architectural Description Language                              |

| ECU         | Electronic Control Unit                                              |

| EMF         | Eclipse Modelling Framework                                          |

| EMOF        | Essential Meta-Object Facility                                       |

| FPGA        | Field-Programmable Gate Array                                        |

| GMP         | Generic Methodology Pattern                                          |

| ID          | Identification                                                       |

| IEC         | International Electrotechnical Commission                            |

| JAXB        | Java Architecture for XML Binding                                    |

| MDA         | Model Driven Architecture                                            |

| MDE         | Model Driven Engineering                                             |

| MIRA        | Model-based Requirements Analysis                                    |

| MOF         | Meta Model Facility                                                  |

| NI          | Network Interface                                                    |

| ΝοϹ         | Network on Chip                                                      |

| OMG         | Object Management Group                                              |

| PIM         | Platform Independent Model                                           |

| PLD         | Programmable Logic Device                                            |

| PSM         | Platform Specific Model                                              |

| QVT         | Query/View/Transformation                                            |

| SDK         | Software Development Kit                                             |

| SIL         | Safety Integrity Level                                               |

| STNoC       | System on Chip                                                       |

| TADL        | Timing-Augmented Description Language                                |

| ΤΙΜΜΟ       | TIMming MOdel                                                        |

| TIMMO-2-USE | Timing Model – TOols, algorithms, languages, methodology, USE cases. |

| TTE         | Time Triggered Ethernet                                              |

| VL          | Virtual Link                                                         |

| VLID        | Virtual Link ID                                                      |

| WCET        | Worst Case Execution Time                                            |

| WCTT        | Worst Case Traversal Time                                            |

| XCM         | Extended Configuration Management                                    |

XMLExtensible Markup LanguageXSDXML Schema

## **1** Introduction

## **1.1 Context**

The objective of DREAMS is to develop a cross-domain architecture and design tools for networked complex systems where application subsystems of different criticality, executing on networked multi-core chips, are supported. DREAMS will deliver architectural concepts, meta-models, virtualization technologies, model-driven development methods, tools, adaptation strategies and validation, verification and certification methods for the seamless integration of mixed-criticality to establish security, safety, real-time performance as well as data, energy and system integrity.

Engineering of safety systems typically implies enforcing a strict development process. V-shape processes have been used frequently to attain certification.

## **1.2 Objectives of the document**

This delivery will define a DREAMS development process that is realized on the top of DREAMS platform with the building blocks from WP2-WP5 and which will be applied in the way that will be possible, on the DREAMS three demonstrators (WP6-WP8). The overall development process, which is based on IEC 61508, will be complemented by abstracting the different aspects that must be covered by the models, the models used in individual domains, and the necessary tool support for model-to-model transformation, verification and code generation.

## **1.3 Structure of the document**

This document contains the following structure. Section 2 describes the approaches to safety (IEC 61508), security and timing for development of DREAMS project based development process. Section 3 describes the required meta-models and model transformations for a tool-supported workflow. Finally Section 4 provides a relation matrix of requirements and sections related with these requirements.

## 1.4 IEC 61508 Safety Life Cycle Overview

A safety life cycle is a series of phases from initiation or specification of safety requirements, to cover and develop of safety features in safety-critical system, and ending in decommissioning of that system. The IEC 61508 standard covers safety-related systems where a system incorporates electrical/electronic/programmable electronic devices. The standard covers possible hazards caused by failures of the safety functions of E/E/PE safety related systems. The detection of a potentially dangerous condition that results in the action of a protective or corrective mechanism to prevent hazardous events is defined as *functional safety*. IEC 61508 is concerned with the E/E/PE safety-related systems whose failure could have an impact on the safety of persons and/or environment.

The standard has two fundamental points: the safety life cycle and the safety integrity levels. The safety life cycle is defined as a process that includes all necessary steps to achieve the required functional safety.

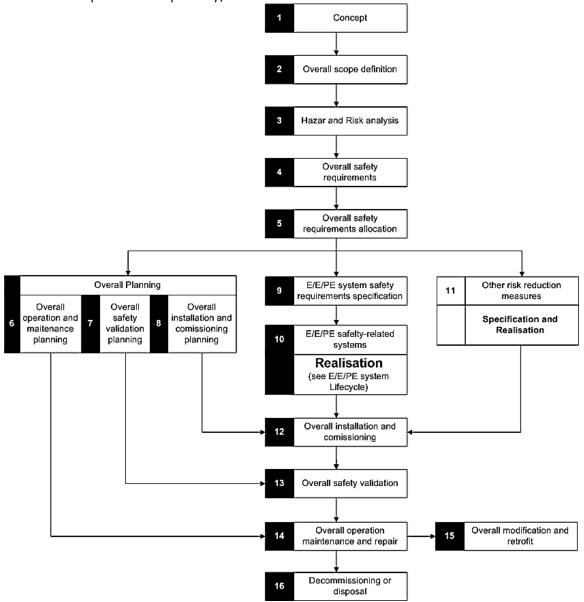

Figure 1 show the safety life cycle defined by IEC 61508 [1], which is basis, followed and complained by the proposed DREAMS development process in Section 2.

Phases 1 and 2 entail the considerations of the safety implications of the EUC and the control systems, at the system level. In Phase 3, first two phases' risk identification and analysis, assessed

against tolerable criteria, are done. In phase 4, the risk-reduction measures of safety requirements are specified, and in phase 5 these are translated into the design of safety functions, which are implemented in safety-related systems, depending on the selected manner of implementation in phases 9, 10 and 11. No claim for safety can be made unless its planning considers the overall safety context reflected in phases 6, 7 and 8. The further phases, phases 12-16 are performed when the system has been built. In Phase 12, the system must be installed and commissioned and in Phase 13, the system is checked to verify that all the safety related requirements have been identified and handled during building and installation. Then the system may be put into operation, where there are safety and maintenance activities. It is also foreseen that the system can be modified during operations and therefore, incorporation of some modifications will be needed. The final phase, phase 16, is related with the disposal of the system (e.g., separations of the battery or the toxic elements to dispose them separately).

#### Figure 1: Overall Safety Life Cycle.

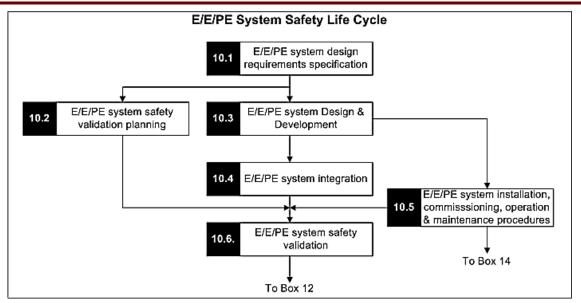

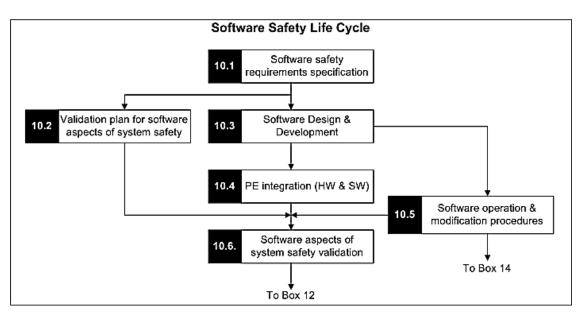

IEC 61508 defines detailed lifecycle stages for stage 10 in the overall life cycle concerned to E/E/PE and software systems developments. The E/E/PE system and software safety life cycles that shall be defined and used according to IEC 61508 are specified in Figure 2 and Figure 3.

Figure 2: E/E/PE Safety Life Cycle.

Figure 3: Software Safety Life Cycle.

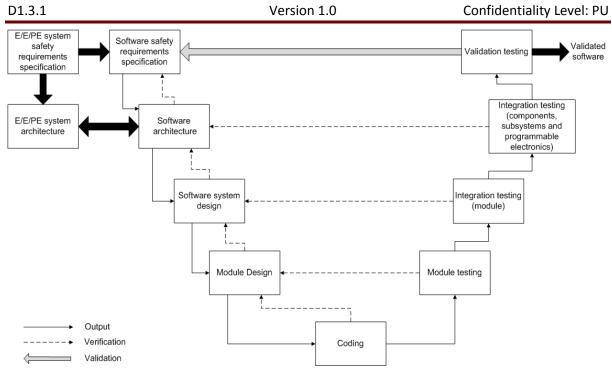

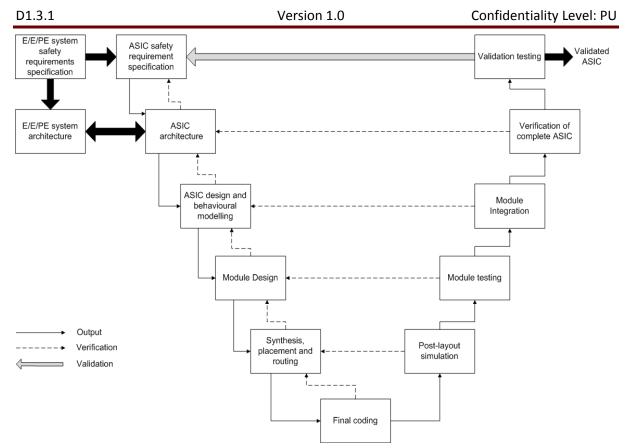

Figure 4 shows the V-model of the development life cycle for the design of ASICs. For IEC 61508, the term ASIC covers standard integrated circuits, core-based and cell-based ASICs, gate arrays, FPGAs, PLDs and CPLDs (IEC 61508-4 3.2.15). As shown, there are similarities between ASIC and software safety life-cycles.

Figure 4: Software Development Process (V-model).

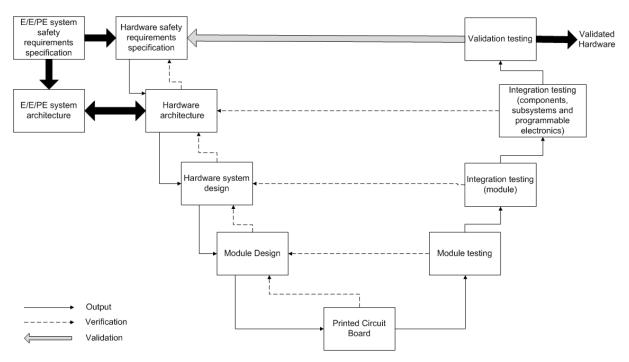

Figure 5: Hardware Development Process (V-model).

Figure 6: ASIC development safety life cycle (V-model).

If another safety life-cycle is used, it shall be specified as part of the management of functional safety activities (clause 6 of IEC 61508-1) and all objectives and requirements of all sub-clause of IEC 61508-2 shall be met.

## 2 Definition of DREAMS Development Process

One of the main objectives of the document is to expose the DREAMS development process, which although is not intended to develop hardware in its specific context, is intended to develop software. The main goal is not hardware development, although according to IEC 61508-2, sometimes (e.g., implementation of communication network inside a FPGA (e.g., STNoC)) is considered as HW, so, the development process of DREAMS shall be compatible for hardware and software development.

In this section, overall results of the analysis of the DREAMS project requirements are detailed. Then the impact of the DREAMS approach on the V-model is presented. And finally, the DREAMS projectspecific development process is detailed and explained.

## 2.1 Safety Approach

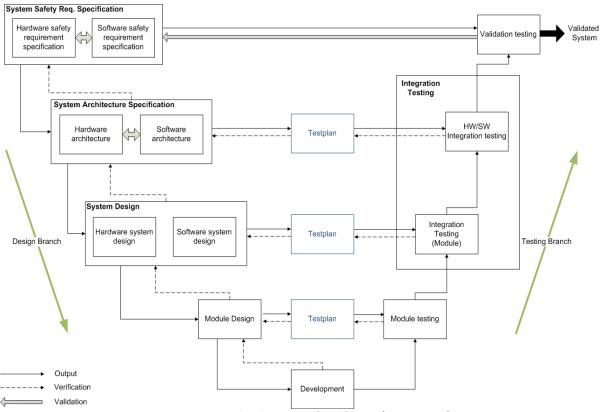

Commonly, V-shape processes have been used to attain certification. IEC 61508 recommends the following V model development process. Figure 7 shows a lifecycle that is composed by two branches: I) a design branch and II) a testing branch. This V-model can be easily customized for any domain (e.g., automotive, railway, etc.).

Figure 7: System development safety lifecycle (the V-model)

The continuous arrows of Figure 7 show the dependencies between phases. At the end of each phase the verification is carried out (discontinuous vertical arrows) against the results of each phase. This is done in order to check the consistency between the inputs and outputs of each phase. As can also be seen, the branches of the Design and Testing are linked by the Test Plans. The solid arrows on the left side of each Test Plan indicate that each test plan, which covers all the requirements, has been generated from the specification of the requirements. Regarding the solid arrows on the right side, these arrows denote the actions to perform the testing. The dashed lines to/from test plans are the verification activities.

In case of hardware development, the techniques and measures defined by IEC 61508-2 must be applied. In case of software development, the techniques and measures defined by IEC 61508-3 must be taken into account.

## 2.1.1 Impact of DREAMS characteristics on the development process

In delivery D1.1.1 the DREAMS project requirements have been collected. The DREAMS project has some requirements that have to be taken into account for the definition of the development process. These relevant requirements are referred to the meet-in-the-middle development approach, traceability and modularity concepts.

| Req. ID  | Description                                                                                                                                                                                               | Reference<br>to               |  |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--|

| R1.8.1   | The architecture should allow design methodologies where top-down and bottom-up design styles are combined.                                                                                               | Meet-in-                      |  |

| R 9.12.1 | The development process should support "top-down" and "bottom-up" development of DREAMS-based applications ("meet-in-the-middle methodology"), if possible aligned with existing practices and workflows. | the-middle<br>developme<br>nt |  |

| R1.1.1  | The architecture shall assure that the behaviour of a subsystem in the value and time domain before integration into a larger systems equals the behaviour after integration.                                                                                     |                   |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| R1.6.1  | The architecture shall leverage multi-core platforms for a system perspective of mixed-criticality applications combining the chip-level and cluster-level.                                                                                                       | Scalability       |

| R 9.9.4 | DREAMS systems need to be automatically adaptive, and this requirement will help automating the production of a configuration in particular in adapting to different platform technologies (e.g. hardware).                                                       |                   |

| R9.6.3  | The meta-models should support the traceability between the artefacts used in the different steps of the development process.                                                                                                                                     |                   |

| R9.13.3 | The development process shall support the traceability for requirements regarding: safety, security, etc.<br>Traceability will help in the avoidance of systematic faults in both HW (IEC 61508-2 Table B.6) and SW (IEC 61508-3 Tables A.1 to A.10) development. | Traceability      |

| R1.10.1 | The architecture shall support different models of computation with corresponding interaction mechanisms on on-chip and off-chip networks: predictable time-triggered communication, event-triggered communication with dynamic arbitration and shared memories.  |                   |

| R1.10.2 | Communication between components in an application subsystem should be performed explicitly using communication primitives provided by the architecture.                                                                                                          |                   |

| R1.10.3 | The architectural style and the development methodology shall consider<br>multiple types of communication and computational activities (periodic,<br>sporadic and aperiodic activities).                                                                          | Heterogen<br>eity |

| R2.7.1  | The on-chip network shall provide different interaction mechanisms required for different models of computation such as Time-Triggered, rate-constrained, best-effort communication and shared memory access.                                                     |                   |

| R 2.7.2 | The architecture shall provide support of different processors and/or hardware accelerators with shared memory access.                                                                                                                                            |                   |

| R4.2.1  | Variability modelling and analysis tools shall be enhanced to achieve by automatic means as well as guided manual means an optimal or best effort configuration of DREAMS platforms and DREAMS systems.                                                           |                   |

| R5.1.1  | Mixed-criticality product line shall be supported to enable certification of product-lines with variability management.                                                                                                                                           |                   |

| R9.9.1  | The variability meta-model shall allow specifying variations of base models in order to define product lines.                                                                                                                                                     | Variability       |

| R9.9.2  | The variability meta-model shall allow to describe different feature sets of applications.                                                                                                                                                                        |                   |

| R9.9.3  | The variability meta-model shall allow to describe different implementation alternatives of applications.                                                                                                                                                         |                   |

| R9.14.1 | The development process shall define how variability is bound.                                                                                                                                                                                                    |                   |

|         | Table 1: Analysis of DREAMS requirements.                                                                                                                                                                                                                         |                   |

Table 1: Analysis of DREAMS requirements.

Below each characteristic of the DREAMS architecture is defined and the respective changes (if necessary) are specified in the development process according to IEC 61508.

## 2.1.1.1 Meet-in-the-middle Methodology

The meet-in-the-middle approach can be considered as a successive refinement method going alternatively from a top-down methodology to a bottom-up methodology, in order to converge into a hardware or software solution. It is this characteristic that makes platform-based design a novel design method, which can be used for the design of complex and heterogeneous embedded systems. The meet-in-the-middle process approach is not a top-down process in which the software is designed in the first place and hardware is developed secondly [2]. It is used when pre-existing products, for which there are some implementations, are partially mapped onto a new service, functionalities or process definition. This option involves the usage of old and new services, functionalities or process definitions. The meet-in-the-middle development strategy offers a middle ground between previous methodologies, that attempts to take advantages of other approaches, while attenuating some of their most notable risks and problems [3]. For attenuation of risks and problems, from the point of view of safety, it is important to show that the existing products are sufficiently free of systematic faults. According to IEC 61508-2 and IEC 61508-3, there are two routes which can be used to probe the non existence of systematic faults.

- **Route**  $2_s^1$  **Proven-in-use approach:** Compliance with the requirement for proven in use elements is established. An element shall only be regarded as proven-in-use when it has a clearly restricted and specified functionality and when there is demonstration that the systematic faults are low enough. (IEC 61508-2 Section 7.4.10)

- Route 3<sub>s</sub> Pre-existing software: This option is the compliance with the requirements of IEC 61508-3, where it is defined that the pre-existing software elements that are reused to implement all or part of the safety functions, shall meet the following requirements:

- $\circ$   $\,$  Meet the requirements of one of the following compliance routes  $\,$

- Route  $1_s$ : compliant development. Compliant with the requirements of the IEC-61508 standard for the avoidance and control of systematic faults in software.

- Route 2<sub>s</sub>: proven in use. Provide evidence that the element is proven in use.

- Route  $3_s$ : assessment of non-compliant development. Compliance with IEC-61508-3 7.4.2.13.

- Provide a safety manual (Annex D of IEC 61508-2 and IEC 61508-3) that gives a sufficiently precise and complete description of the pre-existent elements to make possible an assessment of the integrity of a specific safety function that depends wholly or partly on the pre-existing software elements.

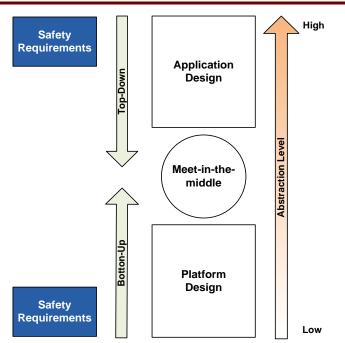

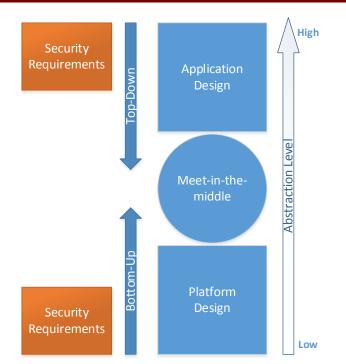

In general, a meet-in-the-middle methodology applies a top-down design (application design) from higher abstraction level and a bottom-up to lower level (platform design). These two processes necessarily meet at some point, when the platform is ready to host an application, and when the application is ready to be hosted in a platform. This point is called meet-in-the-middle point, where performance analysis and architectural exploration takes place.

<sup>&</sup>lt;sup>1</sup> s: Designates systematic safety integrity to distinguish it from Route 1<sub>H</sub> for hardware safety integrity.

Figure 8: Meet-in-the-middle design flow of DREAMS.

Figure 8 illustrates the meet-in-the-middle design flow approach for DREAMS, where, a top-down methodology is applied for higher abstraction levels and a bottom-up methodology is applied to lower abstraction levels. At the same time, at the hardware perspective it supports the bottom-up approach (low to high abstraction level), this way enabling hardware adaptation at design-time as well as at runtime using dynamic and partial reconfiguration.

## 2.1.1.2 Traceability

In order to ensure that the software that results from the life cycle activities meets safety-related requirements, it is essential to ensure the consistency between the life cycle stages. Traceability is the impact analysis to check that the decisions made at an earlier stage are adequately implemented in later stages (forward traceability) and that decisions made at later stage are actually required and mandated by earlier decisions.

According to IEC 61508, the following traceability techniques must be used during the development process of DREAMS for assurance of traceability.

- IEC 61508-2 [4] [4]specifies hardware traceability, which should be between specifications, design, circuit diagram and parts lists. It should be computer-aided and based on defined methods (IEC 61508, table B.6 and section 7.2.2.2 of IEC 61508-2).

- In case of software, traceability is done between all phases of the development process, in compliance also with IEC 61508-3. The following table shows the traceability techniques specified by IEC 61508-3 that are interpreted and is going to be used among phases of DREAMS Development process.

A prerequisite for traceability is, that the requirements can be clearly identified. For this, the requirements usually get a unique identifier. Subsequently, for example, in a tables, the relation between the identifier is shown tracked through the development process (with derived requirements and respective test cases). These mentioned tables have to be reviewed (amongst others) to ensure that all requirements have been considered in the respective development document in the respective development phase.

| Technique                                                                                                                                                                     | Ref.   | Table | Interpretation                                                                                                                                                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Forward traceability between the system safety                                                                                                                                | C 2.11 | A.1   | Review to ensure that all system<br>safety requirements are                                                                                                        |

| requirements and the software safety requirements.                                                                                                                            | 0 2.11 | ,     | addressed by software safety requirements.                                                                                                                         |

| Backward traceability between the safety requirements and the perceived safety needs.                                                                                         | C 2.11 | A.1   | Review to ensure that all software<br>safety requirements are actually<br>needed to address systems safety<br>requirements.                                        |

| Forward traceability between the software safety requirements specification and software architecture.                                                                        | C 2.11 | A.2   | Review to ensure that all software<br>safety requirements are<br>addressed by the software<br>architecture.                                                        |

| Backward traceability between software safety requirements specification and software architecture.                                                                           | C 2.11 | A.2   | Review to ensure that all<br>architecture safety requirements<br>are actually needed to address<br>software safety requirements.                                   |

| Forward traceability between the software safety requirements specification and software design.                                                                              | C 2.11 | A.4   | Review to ensure that all software<br>safety requirements are<br>addresses by the software design.                                                                 |

| Forward traceability between the software design specification and the module and integration tests specifications.                                                           | C 2.11 | A.5   | Review to ensure that a adequate<br>test is planned to examine the<br>functionality of all modules and<br>their integration with<br>appropriately related modules. |

| Forward traceability between the system and<br>software design requirements for<br>hardware/software integration and the<br>hardware/software integration test specifications | C 2.11 | A.6   | Review to ensure that the hardware/software integration tests are adequate/ sufficient.                                                                            |

| Forward traceability between the software safety requirements specification and the software safety validation plan.                                                          | C 2.11 | A.7   | Review to ensure that adequate<br>software validation tests are<br>planned to address the software<br>safety requirements.                                         |

| Backward traceability between the software safety validation plan and the software safety requirements specification.                                                         | C 2.11 | A.7   | Review to ensure that all validation tests are relevant.                                                                                                           |

| Forward traceability between the software safety<br>requirements specification and the software<br>modification plan (including reverification and<br>revalidation)           | C 2.11 | A.8   | Adequate modification<br>procedures to achieve the<br>software safety requirements.                                                                                |

| Backward traceability between the software<br>modification plan (including reverification and<br>revalidation) and the software safety requirements<br>specification          | C 2.11 | A.8   | Adequate modification<br>procedures to achieve the<br>software safety requirements.                                                                                |

| Forward traceability between the software design<br>specification and the software verification (including<br>data verification) plan.                                        | C 2.11 | A.9   | Review to ensure adequate test of functionality.                                                                                                                   |

| Backward traceability between the software verification (including data verification) plan and the software design specification.                                             | C 2.11 | A.9   | Review to ensure that all verification tests are relevant.                                                                                                         |

| Forward traceability between the requirements of IEC 61508-1 Clause 8 and the plan for software functional safety assessment                                                  | C 2.11 | A.10  | Check completeness of coverage<br>of the functional safety<br>assessment.                                                                                          |

Table 2: Traceability of DREAMS Development Process.

## 2.1.1.3 Modularity

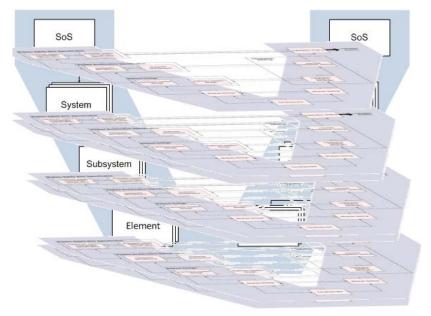

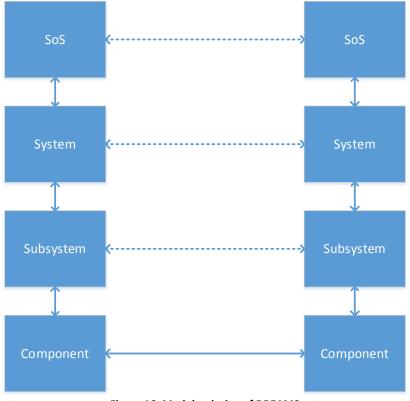

Modular design or modularity in design is an approach that subdivides a system into smaller parts (modules) that can be independently created and then used by different systems to drive different functionalities; a compliant item. The following figure shows the DREAMS modular structure that is decomposed into four levels (System-of-Systems, systems, subsystems and components). A system of system is a composition of independent and interoperable systems intended to achieve unique goals collectively.

For example, considering a series of DREAMS platforms (see D1.2.1, figure 49) as a System of system, the cluster domain can be considered as a system, the Node Domain can be considered as a Sub-System and the Virtualization Layer Domain as an element of the sub-system. In the same way (D1.2.1, figure 50), if we focus on the Node domain, we can consider it as SoS, and its internal elements can be abstracted as systems (e.g., I/O, gateways, applications, etc.), subsystems (e.g., Processor Cores, Local Memory, Network Interface, etc.) and elements (e.g., MON, LRS, Application components).

Figure 9: Modular design of DREAMS.

To apply the modularity approach in the DREAMS development process, IEC 61508 defines some rules, techniques and measures (IEC 61508-2 Annex A-B) that must be followed and used in order to comply with the standard. In case of hardware, IEC 61508-2 defines that modules must be limited by size and must also be isolated. In case of software modification, an impact analysis is carried out to determine how the effect of modifications is limited by the modularity of the overall system.

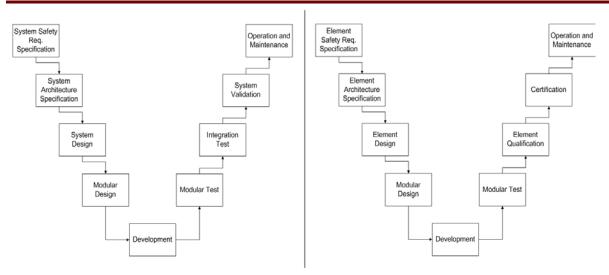

Modularity aims at the decomposition of the software system into small comprehensible parts (element) in order to limit the complexity of the system. It addresses typical development process methods, although there is one difference; a element-based development process focuses on questions related to elements whereas a system development process does not. In that sense, we distinguish the element HW/SW (e.g., dedicated tile/core, etc.) development process and system elements development for the extension of the platform and application elements. The activities or goals of these two processes are different. In case of the system development, the emphasis is to find the proper element and to verify them. In the other hand, in case of the element development, is required the independence and the reusability of the elements.

Figure 10: DREAMS System and Element Development Processes.

Figure 11 shows the DREAMS component-based development process, which assumes that there are closed components (developed elements), that can be integrated into the system through an adaptation process. This way, a element can be reused into diverse systems development at the same time, thereby reducing the required development time and cost.

Figure 11: Component based DREAMS Development process.

Whereas modularity is useful for the decomposition of a system into smaller parts in order to develop independent elements, some features of these elements can be variable, depending of the needs of system/subsystem. Therefore, DREAMS development process also takes into account the variability of both HW and SW. Hardware variability is the ability to change (customize, extend) a hardware platform for a specific context. Software variability is the ability to change (configure,

customize, extend) software artefacts (e.g., code, product, domain requirements, models, design, documentation, test cases) for a specific context. The reusability of any software artefact is determined by its ability to support the variability required from it.

One of the purposes of DREAMS is to offer a core system, whose can be updated and upgraded with specific features, but always with the same nucleus. The conjunction of DREAMS characteristics provide a diverse, independent and re-usable element based architecture, which can be used in future changes or updates (change or update of functionality, platform, etc) of the product line.

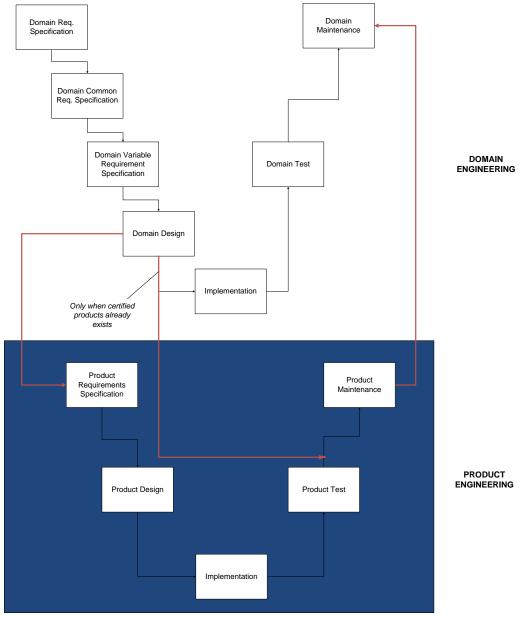

Figure 12: Domain Engineering and Product Engineering.

The process of reusing product-line knowledge in the production of new systems, also called domain engineering, is designed to improve the quality or characteristics of the development through the reuse of artefacts. Domain engineering is applied to all phases of the development process, although it is focused on the three primary phases: Domain analysis, design and implementation paralleling application engineering, which produces a set of implemented components that are relevant to the domain, reusable and configurable. Domain engineering focuses on a family of systems (products).

Figure 12 shows that in domain design, where all domain requirements are available and can be used to define the product specifications. After the product is tested, it can be used for domain implementation together with many other products. The domain implementation must not have direct effect on the product implementation but it has to go back to the domain design and product specification.

## 2.1.2 DREAMS Safety Life-Cycle Specification

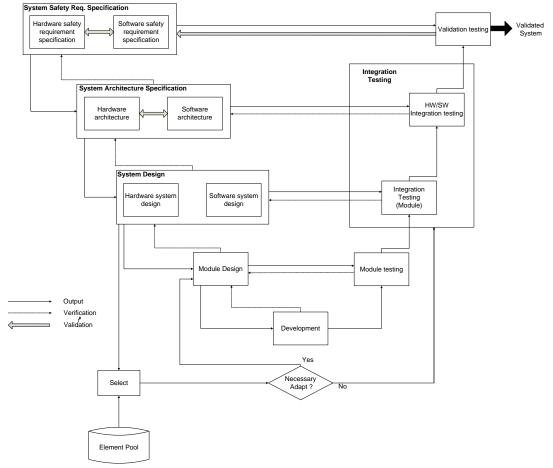

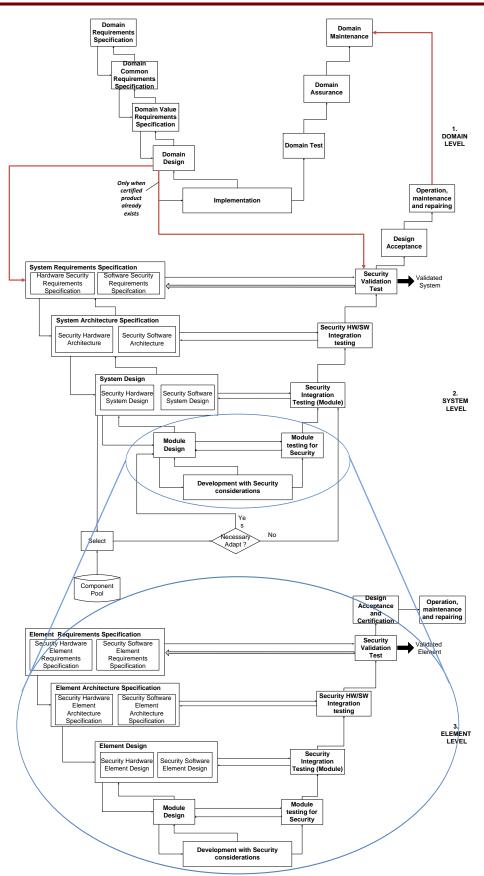

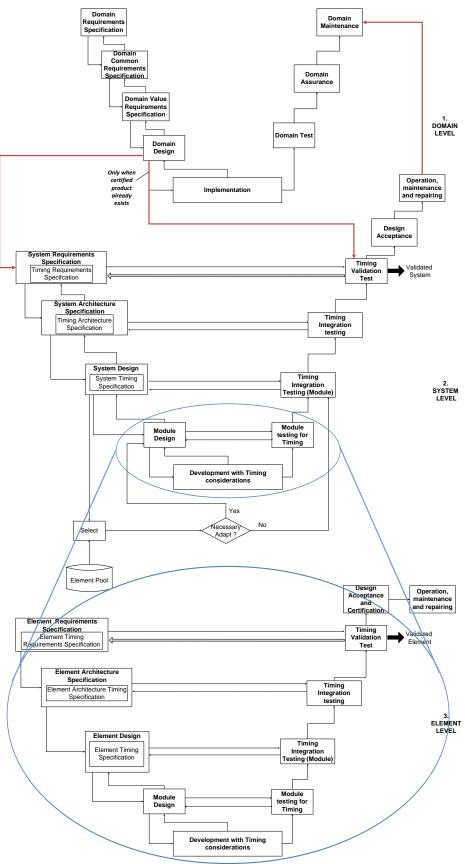

According to points raised in the previous section, this section is intended to summarize the most important aspects of the DREAMS development process related to the safety approach, as shown in Figure 13.

## 2.1.3 Measures for fault avoidance within DREAMS

For each level of Figure 13 (Domain Level, System Level and Element Level) techniques and measures for the avoidance of systematic failures during the different phases of the lifecycle have to be defined. The basis for these techniques and measures are the tables in IEC61508-2 Annex B and IEC61508-3 Annex A, B. Reasonable techniques and measures have to be selected for each phase depending on the selected criticality. In case the criticality level is unclear, the measures for SIL3 shall be selected.

Figure 13: Safety-related Development Process of DREAMS.

## 2.2 Security Approach

As mentioned in 2.1, the V-shape process is used in DREAMS which can be customized for different industrial domains (e.g., avionics, wind power, healthcare). This is due to the fact that the engineering of safety systems implies enforcing a strict development process and V-shape processes have been used frequently to attain certification in the safety domain. However, the engineering of security systems is not based on the V-Model. In the IT security domain, the evaluations for certification are usually based on ISO/IEC 15408, commonly known as the "Common Criteria" [5]. The Common Criteria (CC) supports an objective evaluation of IT products or systems to validate that a particular product or system satisfies a defined set of security requirements. Although the focus of the CC is evaluation, it presents a standard that should be of interest to those who develop security requirements. However, the CC does not give methodological support for security engineering because its focus is on the evaluation of the security of the IT products and is not dependent on the process which is used to develop the product. Integration of security into the software development process is not specified in the CC and therefore any well known industrial approach can be adapted. Nevertheless, the evaluation role of CC makes it of interest to those who develop security products. The Common Criteria allows for seven Evaluation Assurance Levels (EALs). At the time of this writing, CC version 3.1 (revision 4) is in use. Sixteen countries around the world, including many countries of the EU as well as the US, Canada, Japan and Australia, are a part of the Common Criteria Recognition Act (CCRA). This means that the IT products evaluated in one of these countries will be approved in all of the 16 countries. Additionally, the IT products evaluated on the CC approach get certifications which are accepted in 26 countries.

The Common Criteria is flexible in what to evaluate and is therefore not tied to the boundaries of IT products. The CC approach uses Protection Profiles (PP). A PP is an implementation-independent set of security requirements for a class of Targets of Evaluation (TOEs). PP provides customer desires, needs, and requirements on what is needed. PP is used for a Security Target (ST), which states how the PP will be satisfied by the supplier and what will be provided. A TOE is defined as a set of software, firmware and/or hardware, possibly accompanied by guidance that meets specific consumer needs. A TOE can be a complete system or a subsystem. Examples of a TOE are (a) a complete software application, (b) an operating system, (c) the cryptographic co-processor of a smart card integrated circuit or (d) an IT product or system, together with its documentation and administration that is the subject of a CC evaluation. Finally, an Evaluated System (ES) show that the three representations discussed above, i.e., the PP, the ST and the TOE are all consistent.

Though the evaluation and certification of security systems is supported by the CC, the integration of security in the development process of IT systems is missing. Different approaches for secure software development have been proposed in other standards which can be used to achieve security by design. This includes ISO/IEC 27000 [6], ISO/IEC 21827 [7] and the Trustworthy Security Development Lifecycle (SDL) proposed by Microsoft. This also affects the security aspects concerning security requirements and the corresponding security services.

## 2.2.1 Impact of security aspects on the DREAMS development process

The security requirements have been collected in the deliverable D1.1.1. Below the most significant security requirements concerning the development process and model transformation are listed. They are classified into development process, threat model, security requirements, modelling and verification.

| Req.<br>ID | Description                                                           | Reference to |

|------------|-----------------------------------------------------------------------|--------------|

| R11.6.     | Integration of security in the development process, i.e., security by | Development  |

| 1           | design.                                                                  | Process                  |  |

|-------------|--------------------------------------------------------------------------|--------------------------|--|

| R11.1.      | The core security services shall include secure communications,          |                          |  |

| 1           | secure time distribution and secure execution environment.               |                          |  |

| 544.4       | Identification of core and optional security services, security policies | Threat Model             |  |

| R11.1.<br>2 | and threat models in the DREAMS architecture and provision of            |                          |  |

| 2           | security mechanisms to address those identified services.                |                          |  |

| D11.2       | Mechanisms for protection against physical attacks, such as side         |                          |  |

| R11.2.<br>4 | channel attacks, shall be evaluated and provided if found adequate,      |                          |  |

| 4           | e.g., if they do not affect the QoS requirements.                        |                          |  |

| R11.3.      | A choice of cipher suites shall be provided. A cipher suite includes     |                          |  |

| 3           | cryptographic algorithms and their parameters, e.g., key sizes etc.      | <b>a</b>                 |  |

| 544.6       | Core security services on the cluster level shall be identified and      | Security<br>Requirements |  |

| R11.3.<br>4 | provided. This includes services such as end-to-end security (e.g.,      | Requirements             |  |

| 4           | privacy and authentication).                                             |                          |  |

| 544.0       | Key management for secure communication between the entities on          |                          |  |

| R11.3.<br>7 | a cluster shall be provided (Mechanisms for key generation, key          |                          |  |

| /           | distribution/exchange, key destruction etc.).                            |                          |  |

| R9.8.1      | The Security Meta-Model for Data Confidentiality shall allow             |                          |  |

| K9.0.1      | modelling the varying needs of confidentiality.                          |                          |  |

| R9.8.2      | The Security Meta-Model for Data Integrity shall allow modelling the     |                          |  |

| K9.8.2      | varying needs of data integrity.                                         | Modelling                |  |

|             | The Security Meta-Model for Authentication shall allow modelling the     |                          |  |

| R9.8.3      | needs for establishing the authenticity of communication partner and     |                          |  |

|             | the authentication of data origin.                                       |                          |  |

|             | Integrity, authenticity and availability shall be ensured for            |                          |  |

| R11.4.      | communications and communications partners, in the presence of           |                          |  |

| 1           | security threats, such as message sniffing, insertion, modification and  |                          |  |

|             | denial of service.                                                       | Verification             |  |

|             | Security services shall be validated using reasonable attack scenarios   | vermeation               |  |

| R11.4.      | and related penetration tests. Attack scenarios in the context of the    |                          |  |

| 2           | DREAMS architecture need to be envisaged and implemented to              |                          |  |

|             | validate the strength of the security services of DREAMS.                |                          |  |

Table 3: Impact of Security aspects into the DREAMS development process.

## 2.2.1.1 Meet-in-the-middle Methodology

In DREAMS, in order to converge at a final security solution, the security requirements should be fulfilled by the bottom up as well as top down designs. The security requirements should be fulfilled by the platform design as well as the application design to meet at a common middle point. Figure 14 illustrates the meet-in-the-middle design flow approach for DREAMS (section 2.1.1.1). In DREAMS there are various security requirements defined affecting software and hardware. Therefore there are requirements on both design flows, at the top-down design and at the bottom-up design. In the meet-in-the-middle point, all security requirements have to be fulfilled and consistent. This has to be done thoroughly, because attacks on one side could aim on targets on the other side. E.g., a component or module developed for the platform design in the bottom-up could be vulnerable to attacks from a component or module developed in the top-down process for the application design.

Figure 14: Security requirements in the meet-in-the-middle design flow of DREAMS

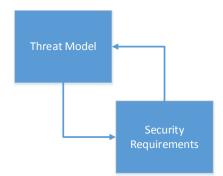

## 2.2.1.2 Threat Model

The security development process uses threat analysis to assess the security needs and identify the security risks. This information is then used to develop security requirements. The security requirements stated in D1.1.1 permit a first view on the security challenges. To get a more detailed view into the security threats, a threat model is needed, which will be an input to the secure development process.

Figure 15: Security Requirements and Threat Model for DREAMS

A threat model describes and analyses the security risks associated with the system. It identifies potential threats to the system and its vulnerabilities. The threat model covers the different individual parts as well as the system in its entirety. Various parts of the system have different attack goals and can lead to diverse benefits for the attacker. Hence, the threat model discusses types of attacks, their functional principles and their impact on the system [8].

Figure 15 shows the relationship between security requirements and the treat model in DREAMS. The threats for the DREAMS architecture identified in the threat model allow a more accurate view on the security requirements. In the threat model, different types of attackers are explained, diverse threats are classified and attack scenarios are illustrated.

The identified threats and attack scenarios can be used to analyse the protection of the system against different attack types in the testing and the verification phase of the development process. This includes different phases like module testing or integration testing.

The threat model and security attacks are described in the deliverable D1.2.1. A thorough analysis and further details for off-chip communication are given in the deliverable D3.3.1.

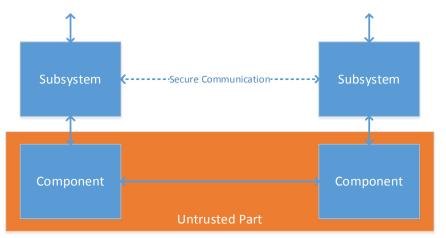

### 2.2.1.3 Security Requirements and Modularity

As mentioned in section 2.1.1.3, modularity is an approach to divide a system into smaller parts to reuse them in different systems. The modular structure of DREAMS is decomposed into the four levels system-of-system, system, subsystem and component (Figure 16), which is related to the architectural style as already discussed in section 2.1.1.3. The use of modular design reduces the interdependence between elements of a system and thus reduces the risk that a change or error in one module will have effects on some or all of the other modules. The security requirements describe demands between modules on the same level. There are end-to-end or point-to-point security requirements. Whereas end-to-end security ensures the provision of the requested security services between these modules, point-to-point security only ensures the provision of the requested security services between two modules on the gath of the communication. E.g., security requirements between two applications are end-to-end requirements and security requirements between two gateways in the communication between two modules are point-to-point requirements.

#### Figure 16: Modular design of DREAMS

However, parts of the system between the modules communicating in a secure way cannot be trusted and have to be treated as insecure. The same applies to the four levels of the modular structure of DREAMS. Underlying modules are not necessarily trustable. Hence, the security services between two modules, e.g., two subsystems, have to assume that there are insecure components.

Figure 17: Modular design example with untrusted components

Figure 17 shows an example for a secure communication between two subsystems. They use the components to communicate with each other, but the components are untrusted. Therefore, the communication does not depend on the underlying components. The subsystems can communicate through a black channel and the channel itself does not have to be considered.

Not every communication has to be secured. Nevertheless, parts of the communication path can use security services anyway. E.g., the communication between two gateways is encrypted, but the communicating applications have not requested the encryption. Otherwise, if they need a specific security service, they cannot assume that the specific security service is provided by a module from a lower level.

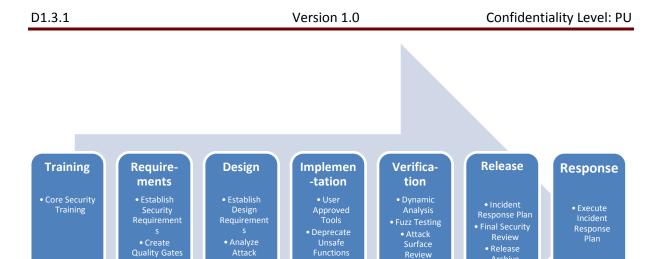

## 2.2.2 DREAMS Security Lifecycle Specification

In order to integrate the security into the software development life cycle of DREAMS, different approaches based on [6, 7, 9] can be considered. The SDL proposed by Microsoft [9] is the most relevant approach to software development based on the V-Model.

The DREAMS security development lifecycle can be roughly based on the Microsoft's SDL as discussed above. The SDL process is depicted in Figure 18.

The core phases of the SDL, i.e., requirements, design, implementation, verification/testing and release roughly correspond to the core phases of the V-Model based software development process.

The SDL integrates effective security practices into each phase of the software development lifecycle to improve awareness of security risks. It is also used to realize time and cost-saving benefits from discovering and eliminating the security issues early in the development process instead of fixing the issues as they are discovered later after the software release. This is more of a security by design approach.

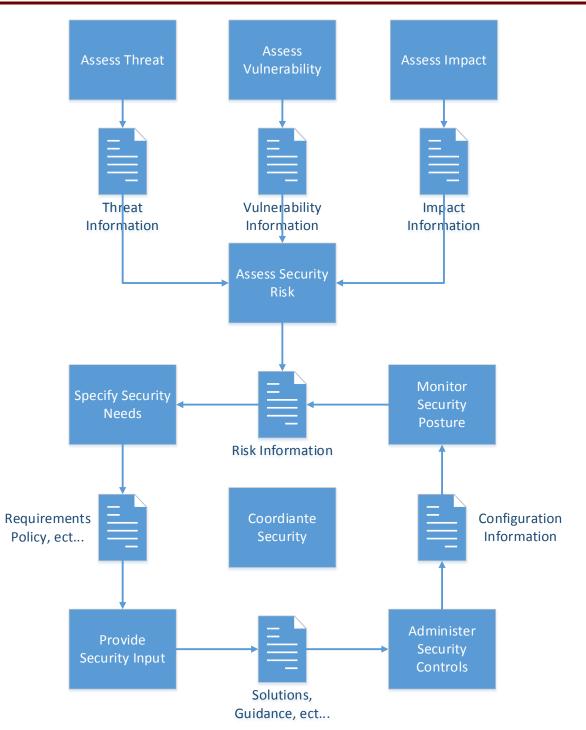

The security approach for the engineering process given in ISO/IEC 21827 [7] is shown in Figure 19. The security engineering process is composed of three main areas, i.e., the risk analysis, engineering and assurance.

/ Bug Bars Security &

#### Figure 18: Trustworthy Security Development Lifecycle (SDL) proposed by Microsoft.

Analysis

Modeling

The risk analysis identifies and prioritizes the dangers inherent to the product or system being developed. Risk assessment is the process of identifying potential problems to the system. Risks are assessed by examining the likelihood of a threat (or vulnerabilities) and by considering the potential impact of an unwanted incident. An unwanted incident is composed of a threat, vulnerability, and impact.

The security engineering works on the produced risk information to find and implement solutions to the problems presented by dangers. Security engineering is a process that proceeds through concept, requirements, design, implementation, testing and deployment phases. Throughout this process, security engineers work very closely with the system engineering team. Coordination between the security and the system development engineers ensure that security is an integral part of the larger process, and not a separate activity. Using the information from the risk process and other auxiliary information such as the relevant laws and policies etc., the security engineers identify security needs together with the customer. This is followed by the identification of specific requirements. The process of proposing solutions to security problems involves identifying possible alternatives and evaluating the alternatives to determining the most promising one. This process is shown in Figure 19.

The assurance process helps the customers in establishing trust in the security solutions. Assurance is defined as the degree of confidence that security needs are satisfied. It is a very important product of security engineering. There are many forms of assurance, e.g., it might be defined as the confidence in the repeatability of the results from the security engineering process. Although assurance does not add any additional controls to counter the risks related to security, but it does provide the confidence that the controls that have been implemented will reduce the anticipated risk.

Any one or both of the above approaches explained above for security engineering can be used in DREAMS for a secure development process. For uniformity with the safety development lifecycle based on the V-Model the best points from the above approaches are integrated into the V-Model as described next.

Figure 19: Security Development Lifecycle based on ISO/IEC 21827

However, the safety engineering process shown in Figure 13 is based on the V-Model. In order to come up with a common approach for the development for DREAMS, the different phases of the proposed security engineering architectures of SDL and ISO/IEC 21827 can be mapped to the various phases of the V-Model based approach shown in Figure 13. Based on the combination of these approaches, the secure engineering approach looks as shown in Figure 20.

Figure 20: Security Development Process of DREAMS

### 2.2.3 Measures for fault avoidance within DREAMS

By following the Security by Design approaches described in the previous section different faults due to security flaws such as DoS attacks, buffer overflow attacks, etc. can be avoided. These need to be considered during the risk analysis phase and the output of the risk analysis should be an input to the secure software engineering phase.

## 2.3 Timing Approach

The consideration of timing constraints and their verification is often neglected but should be considered as a subject on its own: if control orders do not arrive in time at the actuators or are not updated sufficiently often, then the system may get "out of control". The consequences may be damage to the system or harm to people and thus, without considering timing requirements during the development process, it is not possible to design a safe system. However, timing constraints and their verification through prediction techniques such as worst-case analysis or simulation are based on the assumption that in the real system all parts behave as supposed. If at some time an application actually sends its data over a network much more often than foreseen, it may hinder control orders of other applications to arrive in time, which could lead to failures. This is where safety considerations must come into play, in order to establish acceptable failure probabilities, which are then achieved through an appropriate safety design. In this sense, the Safety and Timing approaches are complementary.

The goal of the TIMMO / TIMMO-2-USE (https://itea3.org/project/timmo-2-use.html) projects was to elaborate a meta-model and a methodology for modelling and verifying timing constraints in the automotive domain. The main results, Timing-Augmented Description Language (TADL) and the Generic Methodology Pattern (GMP) for timing, are however general enough to allow their application to other domains. For this reason it is considered in DREAMS as basis for timing considerations.

## 2.3.1 GMP

The Generic Methodology Pattern (GMP) is a set of process steps that identify design tasks that are relevant for considering timing constraints and their validation during the development of electronic systems, see [10].

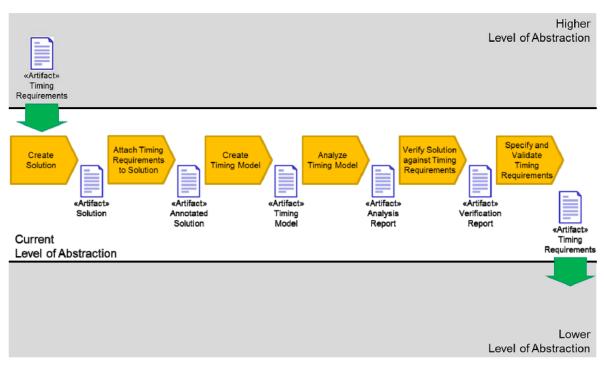

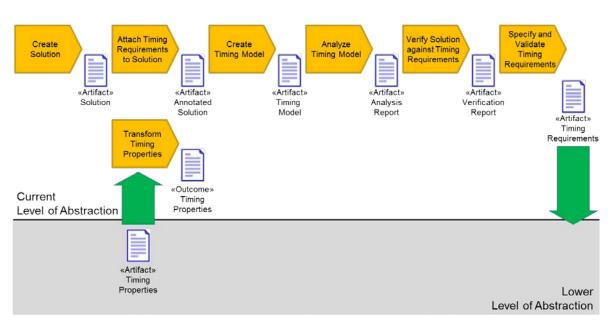

The GMP consists in a generic sequence of tasks that can be executed at every abstraction level of the development process, see Figure 21. These tasks are described in more detail in the following sections.

Figure 21: GMP for Timing

The natural flow of execution is from higher abstraction levels to low abstraction levels, but the GMP can be performed on top-down or bottom-up direction.

#### 2.3.1.1 "Create Solution"

This task describes the definition of solution architecture without any timing information. In the GMP, it is a (big) placeholder for all other design activities at the current design level / system view.

## 2.3.1.2 "Attach Timing Requirements to Solution"

This task "describes the formulation of timing requirements in terms of the current" design level / system view.

This means that for the "input" timing requirements from the previous level/view, the corresponding entities need to be (re)defined in the current view:

- definition of TimingEvents, attached to the structural entities of the current system view

- redefinition of TimingChains in terms of the translated TimingEvents

- redefinition of TimingConstraint with references to the translated TimingEvents

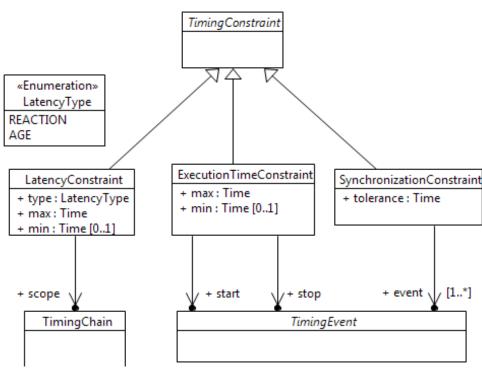

Let us consider the example of latency constraints in the technical view. As explained Section 3.4, a latency constraint is based on a "stimulus" and a "response" event (Figure 36). In the technical view, these TimingEvents would be those related to the reception and the production of data in component ports. As suggested in Section 3.4, these could be called DataReceived (stimulus) and DataSentEvent (response).

#### 2.3.1.3 "Create Timing Model"

This task "describes the definition of a formalized model for the calculation of specific timing characteristics based on properties of the current" design level / system view.

The goal is to define a model (or several models) that will serve as input for the "timing analysis" to be performed in the next task. This may mean to define additional information, like the decomposition of a TimingChain into segments.

Let us return to the latency constraint example, but this time at mapping level. The work of this task would consist in decomposing the "end-to-end" timing chain into segments which span each a different execution / communication perimeter: execution on a tile, communication over NoC, communication over off-chip networks. This decomposition is generally needed so that worst-case analysis or simulation can be applied in order to evaluate timing.

## 2.3.1.4 "Analyze Timing Model"

This task "describes the actual execution and evaluation of all necessary calculations according to the timing model".

This task consists in feeding the analysis tool(s) with the "timing model(s)" built in the previous step, before running the analysis and finally retrieving the results for verification.

#### 2.3.1.5 "Verify Solution against Timing Requirements"

This task "describes the comparison of the obtained analysis results with the specified timing requirements".

The simple part of this task consists in comparing analysis results with requirements.

In our latency constraint example, the verification would consist in simply checking that the upper bound on (end-to-end) delays is smaller than the latency constraint.

Notice however that if several kinds of analyses have been performed, the results might first have to be merged, before being able to perform the simple comparison. If two algorithms produce upper bounds on Worst Case Traversal Time (WCTT), and if algorithm 1 provides a bound larger than the constraint, then it can only be concluded that we algo1 cannot prove that the WCTT are below the constraint. But if for the same WCTT algorithm 2 provide a bound below the constraint then it can be concluded that the constraint is met. The problem with algorithm 1 is simply that the provided upper bound on WCTT is too pessimistic to allow a positive conclusion. The merging of the analysis result would consist in taking the minimum of the bound computed by the different algorithms.

Notice also that the main objective of this design task is to decide "whether the numbers are good enough for progressing" or "whether those numbers have to be revised". If not, it is necessary to return back to an earlier development step/level (iteration)". The "numbers might not be good enough" if slack is needed for future extensions or in order to compensate for lack of precision in the estimation of timing characteristics.

#### 2.3.1.6 "Specify and Validate Timing Requirements"

This task "describes the identification of mandatory timing characteristics and their promotion to timing requirements for the next development phase".

It is about stating which timing constraints are the inputs for the next design phase and whose satisfaction implies the satisfaction of the original input requirements of the current step. For example, in the case of latency constraints, one can either decide to only keep the end-to-end constraint or to impose sub-latency constraints (=sub-time budgets), for the different perimeters (processing, on-chip-, off-chip networks) that are covered by the end-to-end constraint. In the

second case the solution space is reduced, but the global problem is divided into sub-problems with lower complexity.

### 2.3.2 Impact of DREAMS characteristics on the development process

In the deliverable D1.1.1 the DREAMS project requirements have been collected. Some of these requirements have to be taken into account for the definition of the development process. Regarding the Timing Approach, the relevant requirements are listed in the following table and referred to as the, modularity and timing concepts. Other concept such as meet-in-the-middle development approach, traceability and some requirements of modularity and heterogeneity are listed in Section 2.1.1.

| Req. ID | Description                                                                                                                                                                                                                                                                                                                                                                                 | Reference to                |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| R9.13.5 | Integration of an additional application subsystems into an existing system                                                                                                                                                                                                                                                                                                                 | Modularity /<br>Scalability |

| R 4.4.3 | Methods and tool should at least be suitable for all application domains represented by the demonstrators.                                                                                                                                                                                                                                                                                  | - Heterogeneit<br>y         |

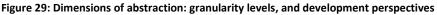

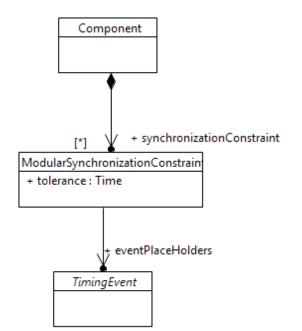

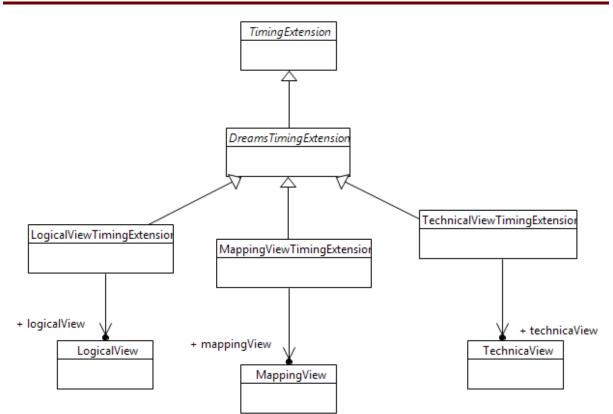

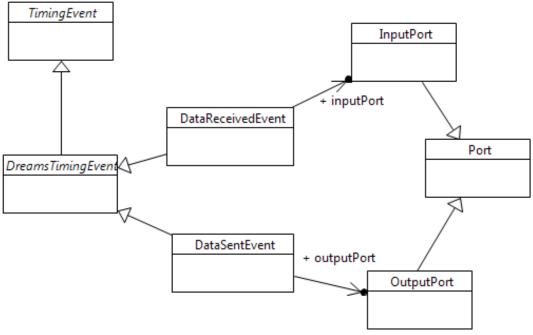

| R 1.2.2 | The architecture shall ensure that all safety-critical subsystems of a system see a sequence of critical events (e.g. reception of messages) in the same order or can re-establish the temporal order.                                                                                                                                                                                      |                             |