# Distributed Real-time Architecture for Mixed Criticality Systems

Fault injection framework D5.2.3

| Project Acronym         | DREAMS           | Grant Agreement<br>Number |         | FP7-ICT-2013.3.4-610640    |       |  |

|-------------------------|------------------|---------------------------|---------|----------------------------|-------|--|

| <b>Document Version</b> | 1.0              | Date                      |         | Deliverable No.            | 5.2.3 |  |

| Contact Person          | Mohammed Abuteir | Organ                     | isation | USIEGEN                    |       |  |

| Phone                   | +49 271 740 2546 | E-Mail                    |         | mohammed.abuteir@uni-siege |       |  |

## Contributors

| Name             | Partner |

|------------------|---------|

| Mohammed Abuteir | USIEGEN |

| Zaher Owda       | USIEGEN |

| Cristina Zubia   | IKL     |

| Félix Casado     | IKL     |

| Marcello COPPOLA | ST      |

| Lukas Kohutka    | ттт     |

| Arjan Geven      | ттт     |

| Jorn Migge       | RTaW    |

| Manuel Muñoz     | FENTISS |

# **Table of Contents**

| Contribu  | tors                                       |                                                                    | 2    |  |  |  |  |  |  |

|-----------|--------------------------------------------|--------------------------------------------------------------------|------|--|--|--|--|--|--|

| Executive | e Sum                                      | nmary                                                              | 8    |  |  |  |  |  |  |

| 1 Intr    | oduct                                      | tion                                                               | 9    |  |  |  |  |  |  |

| 1.1       | Relationship to other DREAMS Deliverables9 |                                                                    |      |  |  |  |  |  |  |

| 1.2       | Posi                                       | tioning of the Deliverable in the Project                          | 9    |  |  |  |  |  |  |

| 1.3       | Stru                                       | cture of the deliverable                                           | 9    |  |  |  |  |  |  |

| Part A: H | Hardw                                      | vare Fault Injection                                               | 11   |  |  |  |  |  |  |

| 2 Rea     | l-Tim                                      | e Fault-Injection Framework                                        | 12   |  |  |  |  |  |  |

| 2.1       | Intro                                      | oduction                                                           | 12   |  |  |  |  |  |  |

| 2.2       | Faul                                       | t Injector Requirements                                            | 12   |  |  |  |  |  |  |

| 2.3       | Faul                                       | t Injector Implementation                                          | 13   |  |  |  |  |  |  |

| 2.3.      | 1                                          | Hardware platform and overall solution                             | 13   |  |  |  |  |  |  |

| 2.3.      | 2                                          | Idle operation                                                     | 15   |  |  |  |  |  |  |

| 2.3.      | 3                                          | Faults injection                                                   | 16   |  |  |  |  |  |  |

| 2.3.      | 4                                          | Software Control                                                   | 18   |  |  |  |  |  |  |

| 2.4       | Eval                                       | uation                                                             | 20   |  |  |  |  |  |  |

| 2.4.      | 1                                          | Set-up                                                             | 20   |  |  |  |  |  |  |

| 2.4.      | 2                                          | Test results                                                       | 21   |  |  |  |  |  |  |

| 2.4.      | 3                                          | Real-Time Fault-Injection Framework in the wind power demonstrator | 24   |  |  |  |  |  |  |

| 3 On-     | chip F                                     | Fault-Injection Framework                                          | . 26 |  |  |  |  |  |  |

| 3.1       | Faul                                       | t injection Emulation Platform                                     | 26   |  |  |  |  |  |  |

| 3.2       | The                                        | Fault Model                                                        | 26   |  |  |  |  |  |  |

| 3.3       | The                                        | DREAMS Fault Injection Emulation Platform                          | 27   |  |  |  |  |  |  |

| 3.4       | Eval                                       | uation                                                             | 31   |  |  |  |  |  |  |

| 3.4.      | 1                                          | Set-up                                                             | 31   |  |  |  |  |  |  |

| 3.4.      | 2                                          | Test description                                                   | 32   |  |  |  |  |  |  |

| 3.4.      | 3                                          | Test results                                                       | 33   |  |  |  |  |  |  |

| 3.5       | Con                                        | clusions                                                           | 33   |  |  |  |  |  |  |

| Part B: 9 | Simul                                      | ation Environment and Fault Injection                              | 34   |  |  |  |  |  |  |

| 4 Vali    | datio                                      | n of the DREAMS Chip Simulation Framework                          | 35   |  |  |  |  |  |  |

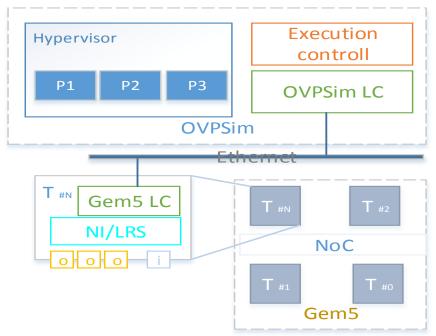

| 4.1       | DRE                                        | AMS Chip Co-Simulation Virtual Platform                            | 35   |  |  |  |  |  |  |

| 4.1.      | 2                                          | Gem5 Configuration and Execution Instructions                      | 38   |  |  |  |  |  |  |

| 4.2       | Synt                                       | hetic Use Case Validation                                          | 38   |  |  |  |  |  |  |

| 5  |    | Simu  | ulatio  | on Fault-Injection Framework                                       | 41 |

|----|----|-------|---------|--------------------------------------------------------------------|----|

|    | 5. | 1     | Faul    | t Injector Implementation                                          | 41 |

|    |    | 5.1.3 | 1       | Omission Failure                                                   | 41 |

|    |    | 5.1.2 | 2       | Corruption                                                         | 41 |

|    |    | 5.1.3 | 3       | Link Failure                                                       | 42 |

|    |    | 5.1.4 | 4       | Crash Failure                                                      | 42 |

|    |    | 5.1.  | 5       | Delay Failure                                                      | 43 |

|    |    | 5.1.0 | 6       | Babbling idiot Failures                                            | 43 |

|    |    | 5.1.  | 7       | Masquerading Failure                                               | 43 |

|    | 5. | 2     | Eval    | uation                                                             | 43 |

|    |    | 5.2.2 | 1       | Simulation Framework in the avionic demonstrator                   | 44 |

| 6  |    | Imp   | leme    | ntation of Model-Driven Configuration for the Simulation Framework | 47 |

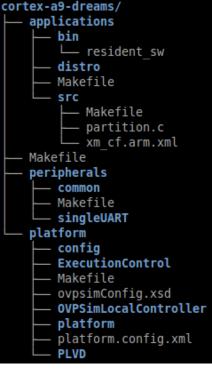

|    | 6. | 1     | How     | <pre>v to Configure and Execute the Generation</pre>               | 47 |

|    |    | 6.1.3 | 1       | Description                                                        | 47 |

|    |    | 6.1.2 | 2       | Relations and dependencies with other tools                        | 47 |

|    |    | 6.1.3 | 3       | Inputs                                                             | 47 |

|    |    | 6.1.4 | 4       | Outputs                                                            | 47 |

|    |    | 6.1.  | 5       | Running the generator                                              | 48 |

|    | 6. | 2     | Cont    | figuration Files for the Cluster Level                             | 53 |

|    |    | 6.2.3 | 1       | Specification of Configuration File Formats with Examples          | 53 |

|    | 6. | 3     | Cont    | figuration Files for the Chip Level                                | 54 |

|    |    | 6.3.2 | 1       | Specification of Configuration File Formats                        | 54 |

| 7  |    | Ana   | lysis d | of Simulation Traces                                               | 57 |

|    | 7. | 1     | Trac    | e Files                                                            | 57 |

|    |    | 7.1.3 | 1       | Off-chip Network Related Events                                    | 57 |

|    |    | 7.1.2 | 2       | On-chip network related events                                     | 57 |

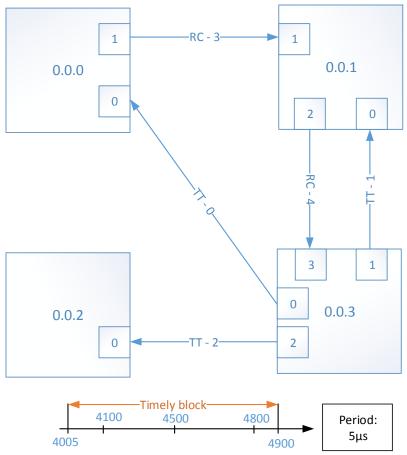

|    | 7. | 2     | Ехро    | ort of DREAMS System Description to RTaW-Timing Tool               | 58 |

|    | 7. | 3     | Visu    | alization of Trace Analysis Results                                | 59 |

|    |    | 7.3.3 | 1       | Frame Drop Tables                                                  | 59 |

| Pa | rt | С     |         | Validation Framework                                               | 60 |

| 8  |    | Valio | datio   | n Framework                                                        | 61 |

|    | 8. | 1     | Valio   | dation Methodology                                                 | 61 |

|    |    | 8.1.3 | 1       | Hardware Testing Strategy                                          | 61 |

|    |    | 8.1.2 | 2       | Test Bench Concept                                                 | 62 |

|    |    | 8.1.3 | 3       | Modeling Concept                                                   | 62 |

| 8.1.4   | CLK model                                 | 63 |

|---------|-------------------------------------------|----|

| 8.1.5   | RESET model                               | 64 |

| 8.1.6   | DIO model                                 | 64 |

| 8.1.7   | GMII MON model                            | 65 |

| 8.1.8   | GMII GEN model                            | 65 |

| 8.1.9   | RMII MON model                            | 66 |

| 8.1.10  | RMII GEN model                            | 66 |

| 8.1.11  | AHB HOST model                            | 67 |

| 8.2 Imp | lementation of the Validation Methodology | 68 |

| 8.2.1   | Test Procedure Synchronization            | 68 |

| 8.2.2   | Test Procedure Freedom from Interference  | 69 |

| 8.2.3   | Test Procedure Security                   | 69 |

# Table of Figures

| Figure 1 Sketch of the Fault Injector Deployment                                               | 13 |

|------------------------------------------------------------------------------------------------|----|

| Figure 2 Sketch for masquerading fault                                                         | 15 |

| Figure 3 ChipScope capture of Idle Operation                                                   | 16 |

| Figure 4 ChipScope capture of Byte Modification                                                | 17 |

| Figure 5 ChipScope capture of Frame Delay                                                      | 17 |

| Figure 6 ChipScope capture of Frame Loss                                                       | 18 |

| Figure 7 Graphical User Interface (GUI)                                                        | 19 |

| Figure 8 Validation setup                                                                      | 21 |

| Figure 9 Byte Modification (BM) fault                                                          | 22 |

| Figure 10 Frame Delay (FD) fault                                                               | 23 |

| Figure 11 Frame Loss (FL) fault                                                                | 24 |

| Figure 12 Evaluation of the Real-time Fault-Injection Framework in the wind power demonstrator | 25 |

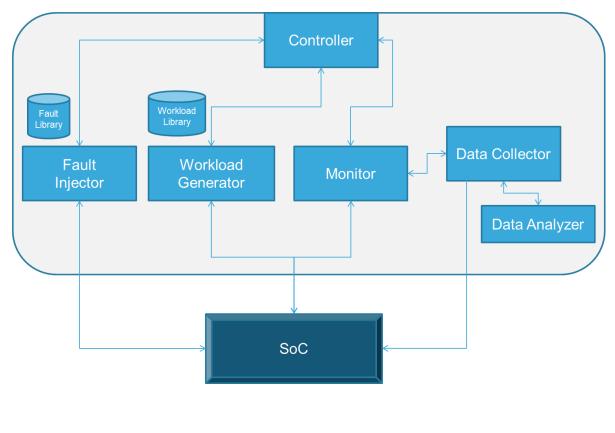

| Figure 13 Fault Injection Framework                                                            | 28 |

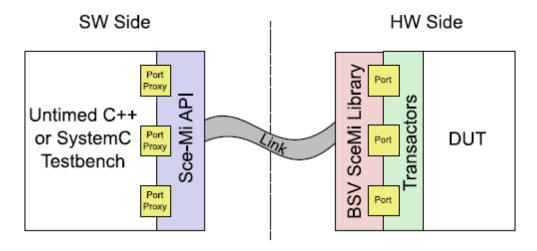

| Figure 14 SCEMI API                                                                            | 30 |

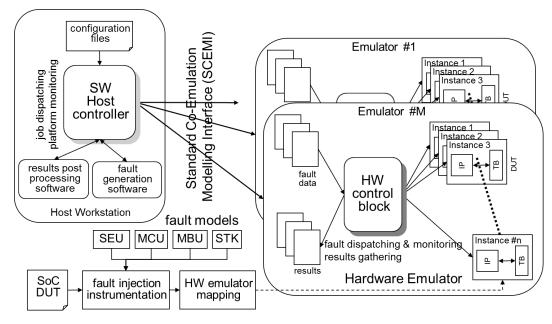

| Figure 15 Emulation Platform                                                                   | 30 |

| Figure 16 STNOC DREAMS instance                                                                | 31 |

| Figure 17: DREAMS Chip Co-Simulation Virtual Platform                                          | 35 |

| Figure 18: OVPSim contents tree                                                                | 36 |

| Figure 19: Xtratum platform configuration                                                      | 37 |

| Figure 20: Gem5 Execution Command Including Generic Configurations                             | 38 |

| Figure 21: Synthetic Use Case Design and Configuration                                         | 39 |

| Figure 22: Beginning of the Gem5 simulation output                                             | 39 |

| Figure 23: OVPSim simulation output                                                            | 40 |

| Figure 24: use case termination statistics (Gem5 side)                                         | 40 |

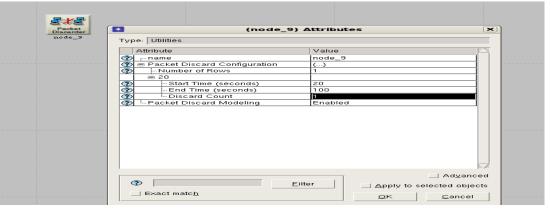

| Figure 27: Packet Discarder with Attributes                                                    | 41 |

| Figure 28 : Link Configuration with Attributes                                                 | 42 |

| Figure 29: Failure Recovery with Attributes                                                    | 42 |

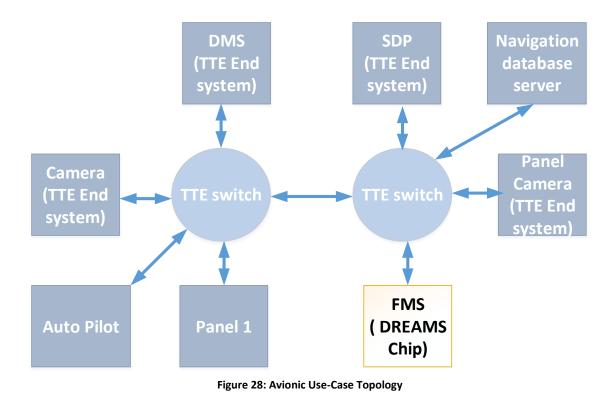

| Figure 30: Avionic Use-Case Topology                                                           | 44 |

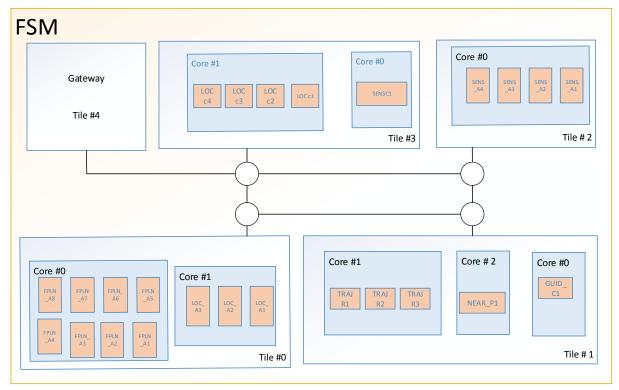

| Figure 31: FMS                                                                                 | 45 |

| Figure 32: Structure of virtual platform configuration file set                                | 48 |

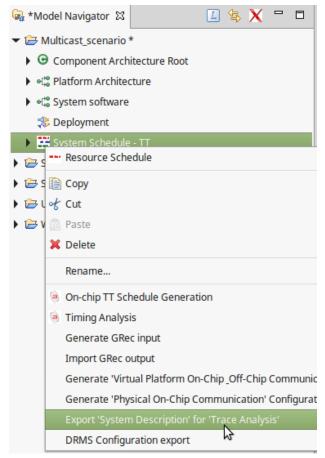

| Figure 33: Context menu for generating the configuration files for the virtual platform        | 49 |

| Figure 34: Specifying the duration of message injection                                        | 49 |

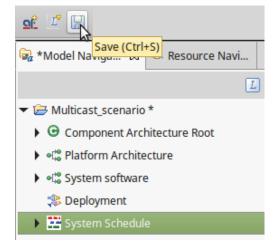

| Figure 35: Persisting the generated configuration model                                        | 50 |

| Figure 36: Switching to the "Resource Navigator"                                               | 50 |

| Figure 37: Visualizing the generated configuration model                                       | 50 |

| Figure 38: Visualization of configuration model items                                          | 51 |

| Figure 39": "Run Configuration Generation Framework" menu entry                                | 52 |

| Figure 40: Selection of the configuration files to generate                                | 53 |

|--------------------------------------------------------------------------------------------|----|

| Figure 41: Example of a switch configuration file                                          | 53 |

| Figure 42: Example of the configuration file for nodes without NoC                         | 54 |

| Figure 43: Example of the on-chip/off-chip gateway configuration file for RC virtual links | 54 |

| Figure 44: Example of the on-chip/off-chip gateway configuration file for TT virtual links | 54 |

| Figure 45: Example of the port configuration file                                          | 55 |

| Figure 46: Example of the serialization unit configuration file                            | 55 |

| Figure 47: Example of the message injection configuration file                             | 56 |

| Figure 48: Frame drop events                                                               | 57 |

| Figure 49: Export of system description for trace analysis                                 | 58 |

| Figure 50: Visualization of frame drop statistics                                          | 59 |

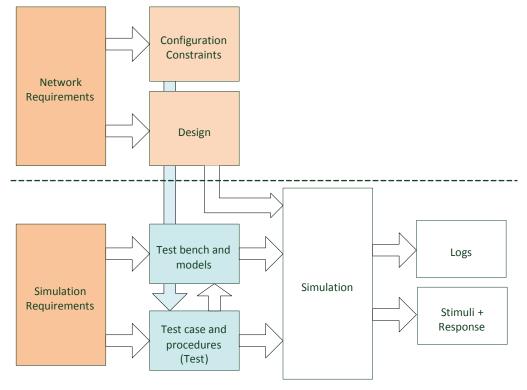

| Figure 51: Overall Validation Strategy                                                     | 61 |

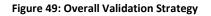

| Figure 52: Overview of the basic Verification Concept                                      | 62 |

| Figure 53: Simulation models and interaction with DUT                                      | 63 |

| Figure 54 Network topology and data flow in DUT                                            | 68 |

| Figure 55: Simulated network topology and data flow for synchronisation validation         | 69 |

## **Executive Summary**

This deliverable presents the fault injection and validation framework of DREAMS. The fault injection framework serves for verifying the DREAMS architecture using hardware fault injection and simulations. The fault injection comprises two dimensions, namely cluster level fault injection and chip level fault injection.

- Hardware fault injection at cluster level: The hardware fault injector at the cluster level aims at testing the proper operation of a safety communication layer. The fault injector has been developed using a ZedBoard, which includes programmable logic (programmed using VHDL language) and an ARM processor (programmed using C language). Moreover, an expansion FMC board with two Ethernet ports to access the medium has been added. The whole system is controlled by a PC (with a C# application) that commands the fault injector through the ZedBoard's ARM via its Ethernet port.

- **Fault injection in simulation at cluster level**: The fault injection at cluster level in the simulation was developed to simulate the system behaviour under the effects of design faults and operational faults. Thereby, the simulation framework supports the quantitative evaluation of the reliability of a DREAMS system with subsystems of different criticality.

Moreover, the validation framework has been developed based on the low-level simulation of the communication between different DREAMS nodes to perform logic simulation. These low-level simulation models aim at finding potential errors in the implementation of protocols and standards in hardware.

• Hardware fault injection and simulation at chip level: The hardware fault injection at the chip level was implemented to check failures according to the SoC under test specification, which gives the ability to increase the failure robustness for Functional Safety. Additionally, a novel definition of a framework that introduces the fault injection mechanisms in the current emulation flow is given in this deliverable.

The fault injection and validation framework is configured using the model-based configuration tools from WP4. Tool support is also provided for the visualization and analysis of the trace analysis results.

## **1** Introduction

This deliverable is dedicated to the implementation of the fault injection framework. The fault injection framework has been implemented at different levels, i.e. hardware fault injection at the cluster level and chip level as well as fault injection in simulations. To validate the reliability of the DREAMS architectures, different use-cases have been used.

In order to seamlessly integrate the virtual platform into the DREAMS tool chain, a model-driven configuration file generator has been implemented. Its goal is the automatic creation of simulator configuration files from a given system description in order to avoid error-prone manual editing. Furthermore, to ease the analysis of simulation results, high-level properties such as end-to-end delays have been synthesized out of simulation traces.

Furthermore, a formal validation framework has been implemented for mapping of simulation results to hardware to provide an end-to-end simulation environment that detects errors that cannot be found by simulating only the components.

## **1.1 Relationship to other DREAMS Deliverables**

The hardware building blocks that have been implemented within WP2 and WP3 were the main input for the fault injection to validate and test different hardware building blocks such as STNoC and EtherCAT components. The virtual platform that was implemented in T5.2 served as the primary input for the fault injection in simulations. The fault injection framework will be used in different use-cases from WP6 and WP7.

The meta-model (T1.4 & T1.6) was the main input for the model-driven configuration of the simulation building blocks. This was developed in cooperation with WP4.

The validation framework is used to evaluate the functionality of the hardware components that are implemented within WP3 such as the gateway and the switch.

## **1.2** Positioning of the Deliverable in the Project

The goal of task T5.2 "Simulation, verification and fault-injection framework" is to provide a framework for simulating and verifying the behavior of a mixed-criticality system based on the DREAMS architecture. To achieve this goal, task T5.2 is divided into three deliverables: D5.2.1, D5.2.2 and D5.2.3.

- D5.2.1 Specification of simulation framework

- D5.2.2 Prototype implementation of simulation framework for DREAMS architecture

- D5.2.3 Fault injection framework

This document is the final deliverable of task T5.2. The dissemination level of this deliverable is public (PU) i.e. once approved by the European Commission (EC), it will be freely available for download through the DREAMS project website (http://dreams-project.eu).

## **1.3 Structure of the deliverable**

The remainder of this deliverable is structured in three parts. Part A introduces the implementation of the hardware fault injection. The implementation of the real-time fault injection framework at cluster level is

given in section 2, while the implementation details for the on chip fault injection framework are explained in section 3.

Part B covers the evaluation and validation for the DREAMS simulation environment. The co-simulation of the DREAMS chip with the execution environment is given in section 4. Section 5 describes the implementation of the fault injection in the simulation framework. The detailed specification of the virtual platform configuration file generator is provided in Section 6. The description focuses on the mapping between the DREAMS meta-model entities and the configuration file entities. Section 7 describes the functionalities implemented for the visualization of simulation traces and delay statistics derived from the traces for verification purposes.

Part C provides the description of the validation framework for DREAMS with a new methodology for evaluating the functionality of the hardware components.

# **Part A: Hardware Fault Injection**

## 2 Real-Time Fault-Injection Framework

## 2.1 Introduction

When end-to-end communication takes place, several faults might occur during communication such as transmission errors, repetitions, deletion, delay, etc. An SCL (Safety Communication Layer) has been developed (in WP3) with the intent of considering the communication channel as a black channel and leaving all detection mechanisms in charge of this layer that will isolate the end application from the communication channel faults. The SCL will be stressed in the evaluation plan by means of the real time fault injection framework. The design and development of this Fault-Injector is the topic of this section.

## 2.2 Fault Injector Requirements

The main objective of this activity is to develop an FPGA-based system able to inject faults in a communication between two devices by placing it between them. Ideally, the system has to be able to perform an idle state (i.e. the injector forwards the frames received without introducing any perturbation) and start injecting faults when it is commanded to do so via software. At this point, it has to be raised that just one fault can be injected per iteration (an iteration is defined as a complete sequence of frames exchanged by the two devices). Thus, users have to introduce, via software, which type of fault is injected in a specific iteration. In addition, the Fault Injector has to be bidirectional, that is, being able to inject faults in both directions of the communication.

It will be used to test the Safety Communication Layer's (SCL) behavior, which implements the safety measures (techniques) defined by IEC 61784-3-3 to avoid the communication errors listed below and further detailed in deliverable D3.3.1 section 7.1.1.1:

- **Corruption:** Messages may be corrupted due to errors within communication channel participant, due to errors on the transmission medium, or due to message interference.

- **Unintended repetition:** Due to an error, fault or interference, old not updated messages are repeated at an incorrect point in time.

- **Incorrect sequence:** Due to an error, fault or interference, the predefined sequence (for example natural numbers, time references) associated with messages from a particular source is incorrect.

- Loss: Due to an error, fault or interference, a message is not received or not acknowledged.

- Unacceptable delay: Messages may be delayed beyond their permitted arrival time window, for example due to errors in the transmission medium, congested transmission lines, interference, or due to communication channel participants sending messages in such a manner that services are delayed or denied (for example FIFOs in switches, bridges, routers).

- **Insertion:** Due to a fault or interference, a message is inserted that relates to an unexpected or unknown source entity.

- **Masquerading:** Due to a fault or interference, a message is inserted that relates to an apparently valid source entity, so a non safety relevant message may be received by a safety relevant participant, which then treats it as safety relevant.

- Addressing: Due to a fault or interference, a safety relevant message is sent to the wrong safety relevant participant, which then treats the reception as correct.

## 2.3 Fault Injector Implementation

#### **2.3.1** Hardware platform and overall solution

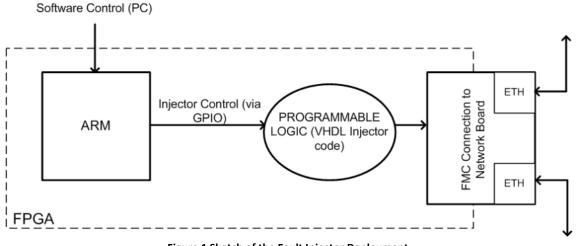

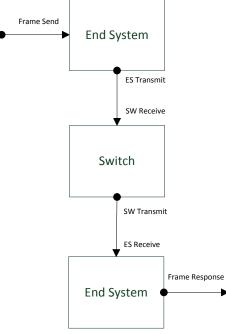

The system has been developed in a ZedBoard<sup>1</sup>, which uses a Network Board (connected via FMC) to access the medium. In Figure 1, a sketch of the system is shown.

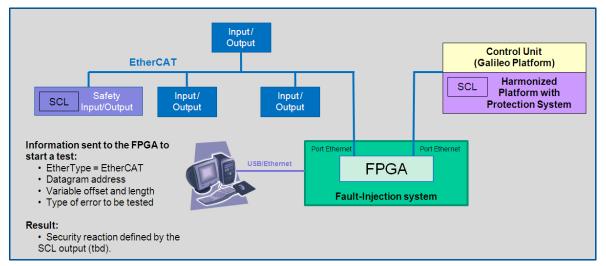

Figure 1 Sketch of the Fault Injector Deployment

The VHDL language has been used for the hardware programming (using Vivado software<sup>2</sup>), and the C language for the software programming and the integration with the hardware part (using SDK software<sup>3</sup>). Additionally, a Graphical User Interface (GUI) has been developed in C# (using Visual Studio Express<sup>4</sup>), in order to provide users with a graphical interface to control the Fault Injector.

In order to fulfill the requirements, three faults have been identified and implemented, which are:

- <u>Byte Modification (BM)</u>: The Fault Injector changes a byte of the original frame. By changing a byte, communication errors such as data corruption and corruption of the sender/receiver addresses are emulated.

- <u>Frame Delay (FD)</u>: The Fault Injector retains a frame and releases it after a certain delay. By delaying frames, it is possible to address the communication error of data packages outside temporal constraints.

- <u>Frame Loss (FL)</u>: The Fault Injector does not forward one of the frames. With this fault, the communication error of a wrong sequence of packages is addressed, as every frame has been generated with its own sequence number.

<sup>&</sup>lt;sup>1</sup> <u>http://zedboard.org/</u>

<sup>&</sup>lt;sup>2</sup> <u>http://www.xilinx.com/products/design-tools/vivado.html</u>

<sup>&</sup>lt;sup>3</sup> <u>http://www.xilinx.com/tools/sdk.htm</u>

<sup>&</sup>lt;sup>4</sup> <u>https://www.visualstudio.com/en-us/products/visual-studio-express-vs.aspx</u>

With these three faults the Fault Injector is capable of reproducing most of the errors listed in section 2.2 as it is shown in the table below.

|                       |                       | Fault techniques     |             |               |                       |                 |            |  |  |  |

|-----------------------|-----------------------|----------------------|-------------|---------------|-----------------------|-----------------|------------|--|--|--|

|                       |                       |                      | mplemented  |               | Π                     | Not implemented |            |  |  |  |

| Error                 | Can it be reproduced? | Byte<br>Modification | Frame Delay | Frame<br>Loss | Unintended repetition | Masquerading    | Addressing |  |  |  |

| Corruption            | Yes                   | x                    |             |               |                       |                 |            |  |  |  |

| Unintended repetition | No                    |                      |             |               | x                     |                 |            |  |  |  |

| Incorrect sequence    | Yes                   |                      | х           |               |                       |                 |            |  |  |  |

| Loss                  | Yes                   |                      |             | х             |                       |                 |            |  |  |  |

| Unacceptable delay    | Yes                   |                      | х           |               |                       |                 |            |  |  |  |

| Insertion             | No                    | -                    |             |               | х                     | х               |            |  |  |  |

| Masquerading          | No                    |                      |             |               |                       | х               |            |  |  |  |

| Addressing            | No                    |                      |             |               |                       |                 | х          |  |  |  |

- <u>Corruption</u>: This fault can be recreated using the fault "Byte Modification" in which the user is allowed to change a packet's byte.

- <u>Unintended repetition</u>: Not implemented.

- <u>Incorrect sequence</u>: It can be reproduced using the "Frame Delay" fault, retaining the message and after a certain time (enough for the subsequent frame to be sent), releasing it.

- <u>Loss:</u> It can be emulated by the "Frame Loss" fault.

- <u>Unacceptable delay</u>: It can be recreated by using the "Frame Delay" fault.

- <u>Insertion</u>: It can be reproduced by changing a byte of the source direction using the "Byte Modification" fault, but the CRC will be wrong and the destination will discard the packet.

- <u>Masquerading</u>: By using the "Byte Modification" fault, a byte of the source direction can be modified. However, with this modification, the CRC computed at SCL level will be automatically wrong and the SCL layer at the destination will discard this packet.

- <u>Addressing</u>: As in the previous case, the destination direction can be changed using "Byte Modification". But, again, the SCL at destination will discard the packet due to a CRC error.

The currently implemented Fault Injector would need some modifications in order to fulfil all the requirements. The pending techniques, which will not be addressed in the current version of the Fault Injector, could be developed in the following way:

<u>Unintended repetition</u>: when the 'Unintended repetition' fault is chosen, as in the case of the 'Frame Delay' fault, the received packed will be stored in memory and will be transmitted after a given amount of time. Unlike the 'Frame Delay' fault, the received packet has to be forwarded. The retransmission time has to be provided by the user.

<u>Masquerading</u>: consider the scenario shown in Figure 1. When the 'Masquerading' fault is chosen, instead of forwarding the packet received from 'Device 1' to 'Device 2', the Fault Injector will generate a 'non-safety' packet with the 0x03 valid source direction.

Figure 2 Sketch for masquerading fault

- <u>Addressing:</u> when the 'Addressing' fault is selected, the Fault Injector will change the original destination address of the received packet by another of an existing device and will also recalculate the CRC. For that purpose a switch will be required in the network as the Fault Injector has just two Ethernet ports.

- <u>Insertion:</u> The Insertion fault will be a combination of 'Unintended repetition' and the 'Masquerading' faults where the source address of the packet stored in memory is changed and the CRC is recalculated.

The implementation of these new techniques in future developments will depend on the needs encountered in the implementation of the SCL and the Fault Injector in the wind power demonstrator, which are not clear yet.

Regarding the control of the Fault Injector, the following signals have been defined:

- Inyectar\_falta: this signal is a flag that indicates when a fault has to be injected.

- Tipo\_falta: used to select the type of the fault: BM, FD or FL.

- Offset: used when BM is selected. Indicates the offset of the byte to be changed.

- Mask\_Mod\_byte: used when BM is selected. The byte modified by BM is the result of the logical xor operation between the original byte and the Mask\_Mod\_byte.

- Delay: used when FD is selected. Specify the amount of time that the frame is retained.

Essentially, the implementation of the Fault Injector has consisted in three main parts, which are: idle operation, fault injection and software control.

#### 2.3.2 Idle operation

As it has been already stated, when no fault is required to be injected, the Fault Injector behavior must be transparent for the communication, that is, the frames received must be automatically forwarded. Thus, the first step in the design has been the access of the medium, which allows the system to receive and transmit frames. Therefore, Medium Access Control (MAC) was required and to that purpose, the "Tri-Mode Ethernet MAC v8.0" (TMAC)<sup>5</sup> Intellectual Property (IP) core has been instantiated. By properly configuring the TMAC, both reception (to the FPGA) and transmission (from the FPGA) are available; thus, four (two for each direction) simple machine states, one for reception and the other for transmission, have been implemented in order to forward the received frames. Those machine states consist of, basically, the required commands to manage the access to a shared memory. In order to avoid any loss as a result of an arrival of frames faster than expected, a circular memory (rather than a fixed one) has been used. This circular memory has been configured to be able to store two frames, which allows the system to store a second frame while the first one is being transmitted.

In Figure 3, it is shown a capture of ChipScope where it can be observed that the data received by the TMAC ('rx\_axis\_mac\_tdata[7:0]') is stored in the circular memory ('dina[7:0]') and, once the frame has been stored ('packet\_stored') it triggers the transmission state machine ('flag\_to\_init\_tx'), so the frame is forwarded from the memory ('doutb[7:0]') to the TMAC ('tx\_axis\_mac\_tdata\_eth2[7:0]'). For this specific scenario, the frames are made up of 61 bytes; thus, with such conditions, the delay introduced by the Fault Injector (i.e. from the time it receives the first byte till it releases the first byte) is approximately 7  $\mu$ s. It has to be noted that the delay is proportional to the frame length. Thus, each additional byte adds a delay of 80 ns.

Figure 3 ChipScope capture of Idle Operation

## 2.3.3 Faults injection

Once the basic part (the idle operation) was built up, the next step was to add the required actions to perform the injection of faults. Indeed, each kind of fault requires specific actions that will shape the Fault Injector.

Byte Modification (BM): When BM is the selected fault, the frame reception works just as in the case of idle operation; so, the major changes have been included in the transmission. Thus, when the byte to be transmitted is in the position indicated by the Offset control signal, instead of transmitting the original byte, the result of the logical xor operation between the original byte and the Mask\_Mod\_byte is sent. In the capture of ChipScope in Figure 4 it can be observed that when 'Inyectar\_falta = 1', 'Tipo\_falta = 1' and 'counter\_tx[11:0] = Offset[11:0]', what is forwarded to the TMAC is not what is stored in memory (x"21") but the result of what is in memory xor 'mask\_mod\_byte[7:0]' => x"21" xor x"DD" = x"FC".

<sup>&</sup>lt;sup>5</sup> <u>http://www.xilinx.com/support/documentation/ip\_documentation/tri\_mode\_ethernet\_mac/v8\_2/pg051-tri-mode-eth-mac.pdf</u>

|                            |       |         |     |     |            |       | 538           |            |             |          |

|----------------------------|-------|---------|-----|-----|------------|-------|---------------|------------|-------------|----------|

| Name                       | Value |         | 520 | 525 | 530        | 535   | 540           | 545        | 550  555    | 5        |

| Unvectar_falta             | 1     | · · · · |     |     |            |       |               |            |             | <u> </u> |

| Offset[11:0]               | 008   |         |     |     |            | 008   |               |            |             |          |

| 🖬 📲 Tipo_falta[1:0]        | 1     |         |     |     |            | 1     |               |            |             |          |

| mask_mod_byte[7:0]         | dd    |         |     |     |            | dd    |               |            |             |          |

| 🖪 📲 doutb[7:0]             | 9b    |         | 44  | S   | 5 66 00    | 21 9  | 0 60 78 4£    | 88 84 3    | d 10 0a 0   | 00       |

| tx_axis_mac_tdata_eth2[7:0 | 9b    |         | 33  | 44  | 55 66 0    | 0 fc  | 9b 6b 78 4    | £ 88 a4    | 2d 10 0a    | 00       |

| \  byte_modified           | 1     |         |     |     |            |       |               |            |             |          |

| 🖬 📲 counter_tx[11:0]       | 009   |         | 003 | 004 | 005 006 00 | 7 008 | 009 00a 00b 0 | 0c 00d 00e | 001 010 011 | 012      |

|                            |       |         |     |     |            |       |               |            |             |          |

Figure 4 ChipScope capture of Byte Modification

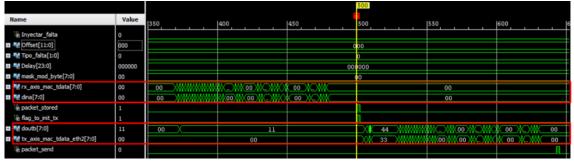

Frame Delay (FD): In case of selecting the FD fault, the received frame is not stored in the circular memory but in a parallel memory and, in addition, a timer is triggered. Once the timer reaches the value indicated by the Delay control signal, a flag is raised in order to transmit the delayed frame. Figure 5 shows two captures of ChipScope where it can be observed that when 'Inyectar\_falta = 1' and 'Tipo\_falta = 2' the data received by the TMAC is not stored in the regular memory but in another one specifically used for delayed frames ('dina\_delay[7:0]'), and that a timer is triggered. When this timer equals the 'Delay[23:0]' signal, the transmission of the delayed frame is triggered ('tx\_delayed\_packet'1); thus, the frame forwarded to the TMAC comes from the memory used to store delayed frames ('doutb\_delay[7:0]').

|                                                                        |          |            |        |      |                                         |        |               |                 | 500         |

|------------------------------------------------------------------------|----------|------------|--------|------|-----------------------------------------|--------|---------------|-----------------|-------------|

| Name                                                                   | Value    |            |        | 400  |                                         | 45     | 0             |                 | 500         |

| 🖟 Inyectar_falta                                                       |          | _ <u> </u> |        |      |                                         |        |               | ·               |             |

| 🛛 📲 Tipo_falta[1:0]                                                    | 2        |            |        |      |                                         | 2      |               |                 |             |

| 🛛 📲 Delay[23:0]                                                        | 989680   |            |        |      |                                         | 989680 |               |                 |             |

|                                                                        | 00       |            |        |      |                                         | 00     |               |                 |             |

| 2 M <mark>rx_axis_mac_tdata[7:0]</mark><br><b>2 M dina_delay</b> [7:0] | 00<br>ff |            | ****** |      |                                         |        | 00 000000     |                 | 00          |

| a dina_delay[7:0] iii packet_stored_delay                              | π<br>1   | 00         |        |      |                                         |        | 00 \\ 00 \\ \ | 00              | <u></u>     |

| <pre>We tx_delayed_packet</pre>                                        | 0        |            |        |      |                                         |        |               |                 |             |

|                                                                        |          |            |        |      |                                         |        |               |                 |             |

|                                                                        |          |            |        |      |                                         |        |               |                 |             |

|                                                                        |          |            | 500    |      |                                         |        |               |                 |             |

| Name                                                                   | Value    |            | 500    | 1520 | 1540                                    | 1560   | 580           | 1600            | 1620 . 1640 |

| 🖟 Inyectar_falta                                                       | 1        |            |        |      |                                         |        |               |                 |             |

| Tipo_falta[1:0]                                                        | 2        |            |        |      |                                         | 2      |               |                 |             |

| 🖬 📲 Delay[23:0]                                                        | 989680   |            |        |      |                                         | 989680 |               |                 |             |

| time_delay[23:0]                                                       | 000000   |            |        |      |                                         | 00000  | 0             |                 |             |

| 1/2 tx_delayed_packet                                                  | 1        |            |        |      |                                         |        |               |                 |             |

| doutb_delay[7:0] tx axis mac tdata eth2[7:0]                           | 11       | 11         |        |      | 000000000000000000000000000000000000000 |        |               |                 |             |

| bx_axis_mac_tdata_eth2[7:0<br>backet_send_delay                        | 0        | 00         | 33     |      | \$00000000⊡                             |        |               | X <u>00</u> XX( |             |

| all pocket_set to_delay                                                | •        |            |        |      |                                         |        |               |                 |             |

|                                                                        |          |            |        |      |                                         |        |               |                 |             |

<u>Frame Loss (FL)</u>: when the FL fault is selected, the reception works just like in the case of idle operation, but the flag to indicate that the frame is ready to be forwarded is never raised. Hence, the stored frame will be overwritten by new frames and will not be transmitted. Figure 6 shows a capture of ChipScope where it can be observed that when 'Inyectar\_falta = 1' and 'Tipo\_falta = 3', the data received by the TMAC is stored in memory, but the flag to start the transmission ('flag\_to\_init\_tx') is never raised, hence, the frame is never transmitted.

|                                  |       |    |     |                                         |     |    |    |     |          |    | 500      |

|----------------------------------|-------|----|-----|-----------------------------------------|-----|----|----|-----|----------|----|----------|

| Name                             | Value |    | 350 |                                         | 400 |    |    | 450 |          |    | 500      |

| 🕼 Inyectar_falta                 | 1     |    |     |                                         | +   |    | ·· |     | <br>     |    | <u> </u> |

| 🖬 📲 Tipo_falta[1:0]              | 3     |    |     |                                         |     | 3  |    |     |          |    |          |

| 🖬 🐏 TRI_MAC/U0/tri_mode_ether    | 00    | 00 | X   | >>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>> |     |    |    | 00  | $\times$ | 00 |          |

| 🖬 🚮 dina[7:0]                    | 00    | 00 |     | 000000000000000000000000000000000000000 |     |    | d  | 00  | $\sim$   | 00 |          |

| light packet_stored              | 1     |    |     |                                         |     |    |    |     |          |    | ٦        |

| <pre>lightering_to_init_tx</pre> | 0     |    |     |                                         |     |    |    |     |          |    |          |

|                                  | 11    | 00 |     | χ                                       |     |    | 11 |     |          |    |          |

| 🖬 👯 tx_axis_mac_tdata_eth2[7:0   | 00    |    |     |                                         |     | 00 |    |     |          |    |          |

|                                  |       |    |     |                                         |     |    |    |     |          |    |          |

Figure 6 ChipScope capture of Frame Loss

## 2.3.4 Software Control

In order to allow users to steer the Fault Injector to their convenience, the control signals are controlled via software. For this purpose, ten "AXI GPIO" IP cores (one for each control signal and for both directions) have been instantiated. Thus, a simple application can be created using SDK in order to initialize and modify the control signals of the Fault Injector. Therefore, the software control part consists of two main parts: Graphical User Interface (GUI) and control data acquisition.

## 2.3.4.1 Graphical User Interface (GUI)

The main purpose of the GUI is to allow users to change the parameters that control the Fault Injector. It has been developed using C#, and its main functionalities are detailed below with a capture (Figure 7) of the implementation as a guide.

| 🖷 Form1                                                                                                                                                |                                                |                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|---------------------------------------------------------------|

| Fault Type Selection<br>Select the fault type:<br>Byte Modification<br>Frame Delay<br>Frame Loss Select<br>Offset<br>Introduce offset value:<br>Submit | Delay<br>Introduce delay (ns) value:<br>Submit | Mask for byte modification<br>Introduce mask value:<br>Submit |

| Fault Inyection Inyect Fault?  Ves  No Network Interface                                                                                               | (Reset) Direction<br>Fault Direction: C        | e Eth1-to-Eth2 in Eth2-to-Eth1                                |

| Console                                                                                                                                                |                                                |                                                               |

|                                                                                                                                                        |                                                |                                                               |

Figure 7 Graphical User Interface (GUI)

The parameters that have to be configured in the GUI are the following ones:

- *Fault Type Selection:* the three faults implemented (BM, FD and FL) are available for users to select one of them.

- *Offset:* Offset for the BM fault.

- *Delay:* the Delay (in nanoseconds) for the FD fault.

- *Mask for byte modification:* the Mask\_Mod\_byte for the BM fault.

- *Fault Injection:* at this point users select if the configured fault has to be injected or not. In order to reset the Fault Injector, after one fault has been injected users have to select No (Reset) and push the 'Update Data button'.

- *Direction:* selection of the communication direction where the fault is to be injected.

- *Network Interface:* by pushing the 'List' button, the available network interfaces are listed, so the most suitable one can be selected.

- *Console:* used by the system to show informative messages.

- *Update Data (button):* when the update data button is pressed the configured fault is sent, via socket, to the control data acquisition program.

#### 2.3.4.2 Control data acquisition

The Control data acquisition is a C++ based program that has been developed using the SDK platform. It is in charge of receiving the configured fault from the GUI and updating the Fault Injector control signals accordingly. Essentially, this program initializes the communication interfaces (from the GUI and to the PL), and remains permanently waiting for any change in the fault configuration. On one hand, the communication between the GUI and the C++ based program is managed through the ZedBoard Ethernet Port. On the other hand, the control signals in the PL are updated through the use of the "AXI GPIO" bus.

To summarize, and gathering all the pieces, the Fault Injector operates as follows: the user configures the control parameters through the GUI (which is running in a PC); and therefore the GUI forwards the data to the control program running in the ARM, which updates the PL transferring the control parameters through the GPIOs.

## 2.4 Evaluation

#### 2.4.1 Set-up

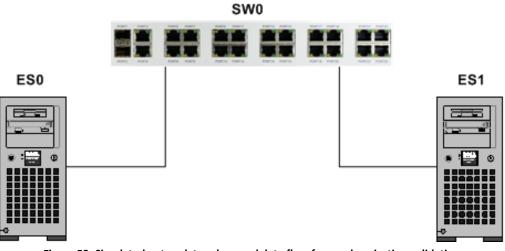

Different tools have been used in order to evaluate the behavior of the Faults Injector. On one hand, Ostinato<sup>6</sup> has been used to generate the traffic that passes through the Fault Injector. On the other hand, Wireshark<sup>7</sup> has been used at the end point in order to gather the traffic that goes through the Fault Injector. In Figure 8 the setup used for the validation is shown. As it can be observed, the setup is made of a PC generating packets with Ostinato, a second PC where users interact with the GUI and a third PC running the Wireshark tool to analyze the packets forwarded by the Fault Injector.

<sup>&</sup>lt;sup>6</sup> <u>http://ostinato.org/</u>

<sup>&</sup>lt;sup>7</sup> <u>https://www.wireshark.org/</u>

Figure 8 Validation setup

#### 2.4.2 Test results

The three types of faults (BM, FD and FL) have been injected so the Fault Injector behavior is checked under all the conditions.

#### 2.4.2.1 BM fault injection

In Figure 9 a BM fault is injected. The Ostinato tool generates 10000 ECAT packets that pass through the Fault Injector and, afterwards, they are gathered in a Wireshark capture. The Fault Injector has been configured with an Offset of 8 and a Mask\_Mod\_byte of 221. It can be observed that the 10000 packets reach the end point and that one of them has a different source direction (Figure 9) as a result of the BM fault.

| Edit V           | ew <u>G</u> o | ⊆aptu  | re 4     | nalyz | te <u>S</u> t | atisti | cs T | elepho                    | ny I | ools | Inte | ernals | Help   |       |       |      |              |     |            |   |     |     |       |      |     |    |       |   |    |   |

|------------------|---------------|--------|----------|-------|---------------|--------|------|---------------------------|------|------|------|--------|--------|-------|-------|------|--------------|-----|------------|---|-----|-----|-------|------|-----|----|-------|---|----|---|

| 0 4              |               |        |          | *     |               | C      |      |                           | -    |      | Ł    |        |        | Ð     | Θ     | m    | FF           | N   |            |   | 34  |     | 1     |      |     |    |       |   |    |   |

|                  |               |        | D (2000) | 0.0   | VGP/          |        | 0 1  | ,                         | -    | U    | -    |        |        | ~     | ~     | ~    |              | -   |            | - | 0.0 | P   |       |      |     |    |       |   |    |   |

| : ecat           |               |        |          |       |               |        |      |                           |      |      |      | ✓ E    | xpress | ion   | Clear | App  | ly S         | ave |            |   |     |     |       |      |     |    |       |   |    |   |

| Tim              |               | Sou    | rce      |       |               |        |      | Destina                   |      |      |      |        |        | ol L  | ength | Info | )            |     |            |   |     |     |       |      |     |    |       |   |    |   |

| 467-23<br>468-23 |               |        |          |       |               |        |      | 11:2<br>11:2              |      |      |      |        | ECA    |       |       |      | Cmds<br>Cmds |     | LRD<br>LRD |   |     |     | LRW   |      |     |    | BRD   |   |    |   |

| 469 23           |               |        |          |       |               |        |      | 11:2                      |      |      |      |        | ECA    |       |       |      |              |     |            |   |     |     | 'LRW  |      |     |    | BRD   |   |    |   |

| 470 23           |               |        |          |       |               |        |      | 11:2                      |      |      |      |        | ECA    |       |       |      |              |     |            |   |     |     | LRW   |      |     |    | BRD   |   |    |   |

| 471 23           |               |        |          |       |               |        |      | 11:2                      |      |      |      |        | ECA    |       |       |      |              |     |            |   |     |     | LRW   |      |     |    | 'BRD' |   |    |   |

| 472 23           |               |        |          |       |               |        |      | 11:2                      |      |      |      |        | ECA    |       |       |      |              |     |            |   |     |     | LRW   |      |     |    | BRD   |   |    |   |

| 473 23           |               |        |          |       |               |        |      | 11:2                      |      |      |      |        | ECA    |       |       |      |              |     |            |   |     |     | 'LRW  |      |     |    | 'BRD' |   |    |   |

| 474 23           |               |        |          |       |               |        |      | 11:2                      |      |      |      |        | ECA    |       |       |      |              |     |            |   |     |     | LRW   |      |     |    | 'BRD' |   |    |   |

| 474 23<br>475 23 |               |        |          |       |               |        |      | 11:2                      |      |      |      |        | ECA    |       |       |      |              |     |            |   |     |     | LRW   |      |     |    | 'BRD' |   |    |   |

| 47525<br>47623   |               |        |          |       |               |        |      | 11:2                      |      |      |      |        | ECA    |       |       |      |              |     |            |   |     |     | 'LRW  |      |     |    | BRD   |   |    |   |

| 477 23           |               |        |          |       |               |        |      | 11:2                      |      |      |      |        | ECA    |       |       |      |              |     |            |   |     |     | 'LRW  |      |     |    | 'BRD' |   |    |   |

| 478 23           |               |        |          |       |               |        |      | 11:2                      |      |      |      |        | ECA    |       |       |      |              |     |            |   |     |     | LRW   |      |     |    | BRD   |   |    |   |

| 479 23           |               |        |          |       |               |        |      | 11:2                      |      |      |      |        | ECA    |       |       |      | Cmds         |     |            |   |     |     | LRW   |      |     |    | BRD   |   |    |   |

| 480 23           |               |        |          |       |               |        |      | 11:2                      |      |      |      |        | ECA    |       |       |      |              |     |            |   |     |     | 'LRW  |      |     |    | 'BRD' |   |    |   |

| 481 23           |               |        |          |       |               |        |      | 11:2                      |      |      |      |        | ECA    |       |       |      |              |     |            |   |     |     | LRW   |      |     |    | 'BRD' |   |    |   |

| 482 23           |               |        |          |       |               |        |      | 11:2                      |      |      |      |        | ECA    |       |       |      |              |     |            |   |     |     | 'LRW  |      |     |    | 'BRD' |   |    |   |

| 483 23           |               |        |          |       |               |        |      | 11:2                      |      |      |      |        | ECA    |       |       |      |              |     |            |   |     |     | 'LRW  |      |     |    | BRD   |   |    |   |

| 483 23<br>484 23 |               |        |          |       |               |        |      | 11:2                      |      |      |      |        | ECA    |       |       |      |              |     |            |   |     |     | 'LRW  |      |     |    | 'BRD' |   |    |   |

| 404 23<br>485 23 |               |        |          |       |               |        |      | 11:2                      |      |      |      |        | ECA    |       |       |      |              |     |            |   |     |     | LRW   |      |     |    | 'BRD' |   |    |   |

| 400 20<br>486 23 |               |        |          |       |               |        |      | 11:2                      |      |      |      |        | ECA    |       |       |      |              |     |            |   |     |     | LRW   |      |     |    | BRD   |   |    |   |

| 486-23<br>487-23 |               |        |          |       |               |        |      | 11:2                      |      |      |      |        | ECA    |       |       |      |              |     |            |   |     |     | LRW   |      |     |    | 'BRD' |   |    |   |

|                  |               |        |          |       |               |        |      |                           |      |      |      |        |        |       |       |      |              |     |            |   |     |     |       |      |     |    |       |   |    |   |

| 488 23           |               |        |          |       |               |        |      | 11:2                      |      |      |      |        | ECA.   |       |       |      |              |     |            |   |     |     | LRW   |      |     |    | BRD   |   |    |   |

| 489 23           |               |        |          |       |               |        |      | 11:2                      |      |      |      |        | ECA    |       |       |      |              |     |            |   |     |     | LRW   |      |     |    | BRD   |   |    |   |

| 490 23           | 2.653         | 429 De |          | b:/   | 8:41          |        |      | 11:2                      | 2:33 | :44  | :55  |        | ECA.   |       | 6.    | L 3  |              | ,   | LRD        | : |     | 1,  | 'LRW  | 1    |     | ь, | BRD   | - | en | 2 |

| ame 4<br>herne   |               |        |          |       |               |        |      |                           |      |      |      |        |        |       |       |      |              |     |            |   |     | 2:3 | 3:44: | 55:0 | 56) |    |       |   |    |   |

| herca            |               |        |          |       |               |        |      |                           |      |      |      |        |        |       |       |      |              |     |            |   |     |     |       |      |     |    |       |   |    |   |

| herca            | T dat         | agram  | (s):     | 3 (   | mds           | , 'L   | _RD' | : le                      | n 1, | 'L   | RW'  | : ler  | n 6,   | BRD   | )': 1 | en   | 2            |     |            |   |     |     |       |      |     |    |       |   |    |   |

|                  |               |        |          |       |               |        |      |                           |      |      |      |        |        |       |       |      |              |     |            |   |     |     |       |      |     |    |       |   |    |   |

|                  |               |        |          |       |               |        |      |                           |      |      |      |        |        |       |       |      |              |     |            |   |     |     |       |      |     |    |       |   |    |   |

|                  |               |        |          |       |               |        |      |                           |      |      |      |        |        |       |       |      |              |     |            |   |     |     |       |      |     |    |       |   |    |   |

|                  |               |        |          |       |               |        |      |                           |      |      |      |        |        |       |       |      |              |     |            |   |     |     |       |      |     |    |       |   |    |   |

| . 11             |               | 44 50  |          | 00    | £             | Ole    | 6 h  | 70 4                      | e 00 | - 4  | 2.4  | 10     | 0.5    | nuf   | Ŀ     |      |              |     |            |   |     |     |       |      |     |    |       |   |    |   |

|                  |               | 44 55  |          |       |               |        |      | 78 4 <sup>.</sup><br>00 0 |      |      |      |        |        | BDUf. |       |      |              |     |            |   |     |     |       |      |     |    |       |   |    |   |

|                  |               | 06 80  |          |       |               |        |      | 00 0                      |      |      |      |        |        |       |       |      |              |     |            |   |     |     |       |      |     |    |       |   |    |   |

|                  |               | 30 01  |          |       |               |        |      | 00 O                      |      |      |      |        |        | 0     |       |      |              |     |            |   |     |     |       |      |     |    |       |   |    |   |

|                  |               |        |          |       |               |        |      |                           |      |      |      |        |        |       |       |      |              |     |            |   |     |     |       |      |     |    |       |   |    |   |

|                  |               |        |          |       |               |        |      |                           |      |      |      |        |        |       |       |      |              |     |            |   |     |     |       |      |     |    |       |   |    |   |

Figure 9 Byte Modification (BM) fault

#### 2.4.2.2 FD fault injection

For this fault, the Ostinato tool is configured to deliver 40 ECAT packets with a rate of 100 ms and the Fault Injector is commanded to introduce a 9.5 ms delay. By taking a look at the time tag of the packets in Figure 10, it is clearly observed that the one marked in blue breaks the pattern by approximately 10ms, which validates the delay introduced by the Fault Injector.

| Edit View Go Capture Analyze Statistics                                                                                                                                       | Telephony <u>T</u> ools Internals <u>H</u> e     | slp.                       |                   |                                |                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|----------------------------|-------------------|--------------------------------|------------------------------|

| ● <b>▲ ■ ▲</b>   <b>B B X 2</b>   <b>Q</b>                                                                                                                                    |                                                  |                            | 🛛 🖾 🖂 🔜           | <b>A</b>                       |                              |

|                                                                                                                                                                               |                                                  |                            |                   | 620                            |                              |

| ecat                                                                                                                                                                          | 💙 Expr                                           | ession Clear Apply         | Save              |                                |                              |

| Time Source                                                                                                                                                                   |                                                  | tocol Length Info          |                   |                                |                              |

| 5 24.1500170 Dell_6b:78:4f                                                                                                                                                    |                                                  | EAT 61.3 Cm                |                   | 'LRW': len 6,                  | BRD': len 2                  |

| 6 24.2500330 Dell_6b:78:4f                                                                                                                                                    |                                                  | EAT 613 Cm                 |                   | 'LRW': len 6,                  | 'BRD': len 2                 |

| 7 24.3498880 Dell_6b:78:4f                                                                                                                                                    |                                                  | CAT 613 Cm                 |                   | 'LRW': len 6,                  | 'BRD': len 2                 |

| 8 24.4500260 Dell_6b:78:4f                                                                                                                                                    |                                                  | EAT 61.3 Cm                |                   | 'LRW': len 6,                  | 'BRD': len 2                 |

| 9 24.5499670 Dell_6b:78:4f<br>10 24.6595290 Dell 6b:78:4f                                                                                                                     |                                                  | IAT 61.3 Cm<br>IAT 61.3 Cm |                   | 'LRW': len 6,                  | 'BRD': len 2                 |

|                                                                                                                                                                               |                                                  |                            |                   | 'LRW': len 6,                  | 'BRD': len 2                 |

| 11 24.7500610 Dell_6b:78:4f<br>12 24.8499710 Dell_6b:78:4f                                                                                                                    |                                                  | IAT 61.3 Cm<br>IAT 61.3 Cm |                   | 'LRW': len 6,<br>'LRW': len 6, | 'BRD': len 2<br>'BRD': len 2 |

| 13 24.9499100 Dell_6b:78:41                                                                                                                                                   |                                                  | LAT 61.3 CM                |                   | 'LRW': len 6,                  | 'BRD': len 2                 |

| 14 25.0499970 Dell_6b:78:41                                                                                                                                                   |                                                  | LAT 61.3 CM                |                   | 'LRW': len 6.                  | 'BRD': len 2                 |

| 15 25.1500770 Dell_6b:78:4f                                                                                                                                                   |                                                  | LAT 61.3 CM                |                   | 'LRW': len 6,                  | 'BRD': len 2                 |

| 16 25.2500920 Dell_6b:78:4f                                                                                                                                                   |                                                  | EAT 61.3 Cm                |                   | 'LRW': len 6,                  | 'BRD': len 2                 |

| 17 25.3500200 Dell_6b:78:4f                                                                                                                                                   |                                                  | TAT 61.3 Cm                |                   | 'LRW': len 6,                  | 'BRD': len 2                 |

| 18 25.4501040 Dell_6b:78:4f                                                                                                                                                   |                                                  | EAT 61.3 Cm                |                   | 'LRW': len 6,                  | 'BRD': len 2                 |

| 19 25.5501150 Dell_6b:78:4f                                                                                                                                                   |                                                  | EAT 61.3 CM                |                   | 'LRW': len 6,                  | 'BRD': len 2                 |

| 20 25.6501090 Dell_6b:78:4f                                                                                                                                                   |                                                  |                            | ds, 'LRD': len 1, |                                | 'BRD': len 2                 |

| 21 25.7501590 Dell_6b:78:4f                                                                                                                                                   |                                                  | EAT 61.3 Cm                |                   | 'LRW': len 6.                  | 'BRD': len 2                 |

| 22 25.8501320 Dell_6b:78:4f                                                                                                                                                   |                                                  | EAT 613 CM                 |                   |                                | 'BRD': len 2                 |

| 23 25.9501500 Dell_6b:78:4f                                                                                                                                                   |                                                  | EAT 61.3 Cm                |                   | 'LRW': len 6,                  | 'BRD': len 2                 |

| 24 26.0501600 Dell_6b:78:4f                                                                                                                                                   |                                                  |                            | ds, 'LRD': len 1, |                                | 'BRD': len 2                 |

| 25 26.1501630 Dell_6b:78:4f                                                                                                                                                   |                                                  | CAT 61.3 Cm                |                   | 'LRW': len 6.                  | 'BRD': len 2                 |

| 26 26.2501990 Dell_6b:78:4f                                                                                                                                                   |                                                  |                            | ds, 'LRD': len 1, |                                | 'BRD': len 2                 |

| 27 26.3500560 pell_6b:78:4f                                                                                                                                                   |                                                  |                            | ds, 'LRD': len 1, |                                | 'BRD': len 2                 |

| 28 26.4502030 Dell 6b:78:4f                                                                                                                                                   |                                                  |                            | ds. 'LRD': len 1. |                                | 'BRD': len 2                 |

| ame 10: 61 bytes on wire (488 b                                                                                                                                               | oits), 61 bytes captured                         | d (488 bits) on '          | interface 0       |                                |                              |

| hernet II, Src: Dell_6b:78:4f                                                                                                                                                 | (00:21:9b:6b:78:4f), Dst                         | :: 11:22:33:44:5           | 5:66 (11:22:33:44 | :55:66)                        |                              |

| herCAT frame header                                                                                                                                                           |                                                  |                            |                   |                                |                              |

| herCAT datagram(s): 3 Cmds, 'LF                                                                                                                                               | RD': Ten 1, 'LRW': Ten 0                         | o, 'BRD': Ten 2            |                   |                                |                              |

|                                                                                                                                                                               |                                                  |                            |                   |                                |                              |

|                                                                                                                                                                               |                                                  |                            |                   |                                |                              |

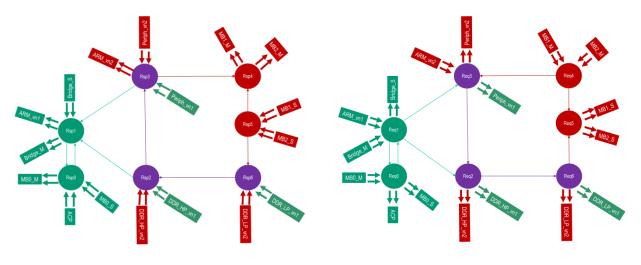

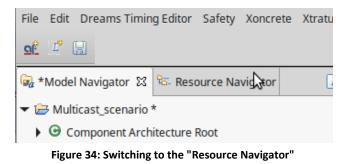

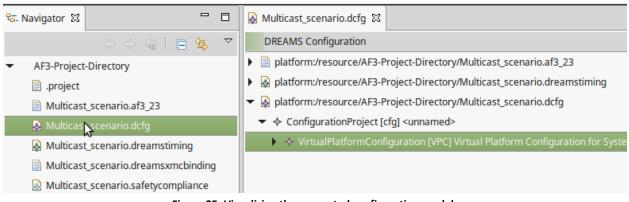

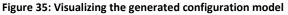

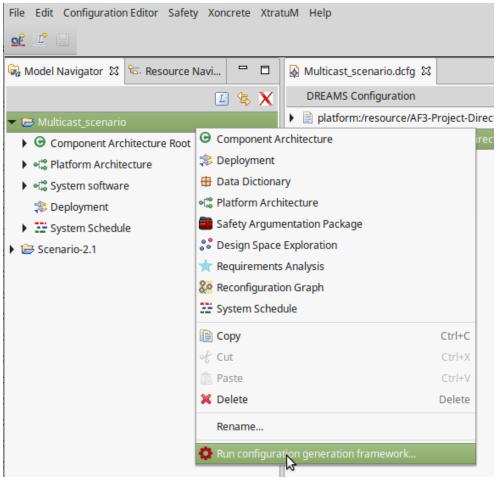

|                                                                                                                                                                               |                                                  |                            |                   |                                |                              |