# Distributed Real-time Architecture for Mixed Criticality Systems

White Paper on Mixed-Criticality Research and Innovation

D9.3.2

| Project Acronym     | DREAMS              | Grant Agreement<br>Number |                       | FP7-ICT-2013.3.4-610640 |        |

|---------------------|---------------------|---------------------------|-----------------------|-------------------------|--------|

| Document<br>Version | 1.0                 | Date                      | September 30,<br>2017 | Deliverable No.         | D9.3.2 |

| Contact Person      | Gautam Gala         | Organisation              |                       | TUKL                    |        |

| Phone               | +49 (0)631 205 2715 | E-mail                    |                       | gala@eit.uni-kl.de      |        |

# Version History

| Version No. | Date       | Change                    | Editor(s)   |

|-------------|------------|---------------------------|-------------|

| 0.1         | 09.07.2017 | initial draft             | Gautam Gala |

| 1.0         | 22.08.2017 | First version             | Gautam Gala |

| 1.1         | 15.09.2017 | Second version            | Gautam Gala |

| 2.0         | 18.09.2017 | Ready for internal review | Gautam Gala |

| R1.0        | 29.09.2017 | Submitted to EC           | Gautam Gala |

# Contributors

| Name                 | Partner         |

|----------------------|-----------------|

| Gautam Gala          | TUKL            |

| Gerhard Fohler       | TUKL            |

| Simon Barner         | FORTISS         |

| Alexander Diewald    | FORTISS         |

| Roman Obermaisser    | USiegen         |

| Thomas Koller        | USIEGEN         |

| Daniel Gracia Pérez  | TRT             |

| Borislav Nikolic     | TU Braunschweig |

| Marcello Coppola     | ST              |

| Miltos Grammatikakis | TEI             |

| Alfons Crespo        | UPV             |

| Javier Coronel       | Fentiss         |

| K. Chappuis          | VOSYS           |

| Gebhard Bouwer       | TUV             |

| Gernot Klaes         | TUV             |

| Jon Perez            | IK4-IKERLAN     |

| Asier Larrucea       | IK4-IKERLAN     |

# Table of Contents

| Ve | ersion                                          | n History                                                                                                                                                                       | 1                                 |

|----|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| Co | ontrib                                          | putors                                                                                                                                                                          | 1                                 |

| Su | ımma                                            | ary                                                                                                                                                                             | 4                                 |

| 1  | Intro<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6 | oduction   Motivation and Objectives   Who Should Read this document?   Related Documents   Essential Characteristics and Role in Future   Related Projects   Document Overview | <b>5</b><br>5<br>5<br>5<br>7<br>9 |

| 2  | <b>Avic</b> 2.1 2.2                             | Defices   Research Challenges   2.1.1   Problems Not Solved in DREAMS   Innovation for Roadmap                                                                                  | <b>11</b><br>11<br>12<br>14       |

| 3  | <b>Auto</b><br>3.1<br>3.2                       | omotive In-Vehicle Networks<br>Research Challenges                                                                                                                              | <b>15</b><br>15<br>17             |

| 4  | Win<br>4.1<br>4.2                               | Ind Power   Research Challenges   4.1.1   Problems Not Solved in DREAMS   Innovation for Road-map                                                                               | <b>19</b><br>19<br>22<br>22       |

| 5  | <b>Hea</b><br>5.1<br>5.2                        | Ilthcare   Research Challenges   5.1.1   Problems Not Solved in DREAMS   Innovation for Road-map                                                                                | <b>24</b><br>24<br>24<br>24       |

| 6  |                                                 | I-time Systems and Scheduling   Research Challenges   6.1.1 Problems Not Solved in DREAMS   Innovation for Road-map                                                             | <b>25</b><br>25<br>28<br>28       |

| 7  | <b>Arcl</b><br>7.1<br>7.2                       | hitectures<br>Research Challenges                                                                                                                                               | <b>30</b><br>30<br>32<br>33       |

| 8                                          | Security                             |    |  |  |  |  |

|--------------------------------------------|--------------------------------------|----|--|--|--|--|

|                                            | 8.1 Research Challenges              |    |  |  |  |  |

|                                            | 8.1.1 Problems Not Solved in DREAMS  | 35 |  |  |  |  |

|                                            | 8.2 Innovation for Road-map          | 35 |  |  |  |  |

| 9 Multicore Chips                          |                                      |    |  |  |  |  |

|                                            | 9.1 Research Challenges              | 36 |  |  |  |  |

|                                            | 9.1.1 Problems Not Solved in DREAMS  | 36 |  |  |  |  |

|                                            | 9.2 Innovation for Road-map          | 36 |  |  |  |  |

| 10                                         | Operating Systems and Hunamiseus     | 38 |  |  |  |  |

| 10                                         | Operating Systems and Hypervisors    |    |  |  |  |  |

|                                            | 10.1 Research Challenges             |    |  |  |  |  |

|                                            |                                      |    |  |  |  |  |

|                                            | 10.2 Innovation for Road-map         | 45 |  |  |  |  |

| 11 Certification, Safety and Dependability |                                      |    |  |  |  |  |

|                                            | 11.1 Research Challenges             | 46 |  |  |  |  |

|                                            | 11.2 Innovation for Road-map         | 50 |  |  |  |  |

| 12 Model-Driven Engineering 52             |                                      |    |  |  |  |  |

|                                            | 12.1 Research Challenges             |    |  |  |  |  |

|                                            | 12.1.1 Problems Not Solved in DREAMS |    |  |  |  |  |

|                                            | 12.2 Innovation for Road-map         |    |  |  |  |  |

|                                            |                                      | 01 |  |  |  |  |

| Bibliography                               |                                      |    |  |  |  |  |

# Summary

Safety-critical systems have become part of our daily life, for example, braking control in cars, controllers in aircrafts, wind turbines and trains, etc. A system failure or malfunction of these systems can cause death, serious injury to people, loss/severe damage to equipment/property, or environmental harm. An increasingly important trend is Mixed Criticality Systems (MCS), which combine safety critical components with components that need a lower level of assurance for failure. With increasing demands from the consumers, services like infotainment that need no certification are also required to be combined with safety critical components.

Design of MCS is becoming increasingly difficult due to adoption of COTS multicore and manycore devices. COTS multicore and manycore device designs are driven by large consumer segments like mobile phones, laptops, etc.; they do not take into account requirements posed by MCS in systems. With increasing demands for connected systems and the emergence of Internet based technologies like cloud computing, loT, etc. and related technologies like Industry 4.0, autonomous cars, etc., the traditionally isolated MCS systems now have to be combine stringent real-time and reliability requirements with the need for an open-world assumption. As a result, they should not only consider safety but also security. The above trends, combined with closed hardware design, have made the process of certification for MCS difficult, expensive and time consuming.

This white paper outlines the research challenges and problems not solved in DREAMS wrt. MCS. It is a result of road-mapping process done during the DREAMS project with inputs from the project partners and the MCS community. It is meant to act as a guide for MCS research in the next 5–10 years.

# 1 Introduction

## **1.1** Motivation and Objectives

One of the key deliverables of the DREAMS Project "White Paper on Mixed Criticality Research and Innovation" is a roadmap for Mixed Criticality Systems (MCS). This white paper is the result of a roadmapping process that took place during the DREAMS project with involvement of project partners and the MCS community. It concisely describes the key research challenges and state-of-the-art in MCS and related application domains. Key challenges to be tackled in coming 5-10 years are described in this document. Moreover, it also gives an overview of problems not solved in the DREAMS project and innovations required to achieve the presented roadmap. The main idea of this white paper is to act like a guide to steer the research efforts by the MCS community.

## 1.2 Who Should Read this document?

This document is not only designed for specialists in the field of MCS but also those seeking to get a general overview of current research in MCS. We believe that anyone who is interested in key challenges in MCS and some of its application domains like Avionics, Wind-power, Healthcare, etc. in the next 5–10 years will find this document beneficial. We have also included some state-of-the-art for each key challenge to give an overview to the reader about the research current state. We also present some innovations in each key area and domain to give an idea to the reader about what is needed to achieve the presented roadmap.

## **1.3** Related Documents

A report [Inf] based on a workshop organized by the European Commission in Feb. 2012 identified the main research challenges in MCS design giving many recommendations defining European research priorities in the medium (3–5 years) and long term (5-10 years). It highlighted the developments in multicore technology and its adoption in MCS resulting in benefits for domains such as automotive and aerospace.

# 1.4 Essential Characteristics and Role in Future

Over the past few years, a trend of integrating components of different criticality levels onto a common hardware platform has evolved in real-time embedded systems. These criticality levels usually express required protection against failure for the corresponding system component to prevent catastrophic consequences; although, they can also include all forms of dependability (availability, integrity, ...). These criticality levels are also know as Development Assurance Level (DAL) in the Avionics domain, or Automotive Safety and Integration Levels (ASIL) in case of Automotive. They need to be followed for certification.

Mixed Criticality Systems (MCS) are embedded systems which have applications of two or more distinct levels of criticality (for example, Low critical and High critical) sharing resources like CPU, memory, communication architecture, etc. MCS have received a lot of attention not only in research

but also in industrial domains like Avionics, Automotive, Healthcare, Windpower, etc. For example, in case of Avionics or Automotive, there are some safety critical application functions like engine control, and many non-safety related functions like infotainment, air-conditioning, etc.

MCS are experiencing a massive paradigm shift to multicore systems as they need more performance and computing resources. Of recent, it has become quite evident that obtaining more performance from single core processors is not possible. Increasing clock frequency is becoming more difficult in embedded systems due to heating problems and energy requirements. Instead of using multiple single core systems, multicore systems have become popular as they can satisfy the required performance and provide reduced size, weight and power consumption (SWAP). But, the market of multicore systems is driven by the consumer market (for example, mobile phones, laptops, etc.), which defines the way these systems are designed. Commercial-of-the-shelf (COTS) multicores are not designed specially with MCS in mind. Hence, there is a need for MCS to adapt to these COTS multicore systems to harness their complete potential.

In addition, the trend of multicore is also evolving into manycore. Manycores are specialized multicores designed for a high degree of parallel processing, containing 10's or 100's or 1000's simpler, independent processor cores. In addition, some multicores have special purpose computing cores (for example for cryptographic algorithms, media processing, etc.) or a field-programmable gate array (FPGA) on the same system on chip (SoC), leading to heterogeneous multicore systems, adding on to In the past, MCS were mainly concerned by safety and reliability the complexity of MCS design. requirements as they were physically isolated and ran on dedicated hardware. But with the advent of Industry 4.0, Cloud Computing and Internet of Things (IoT), it has become important to combine stringent real-time constraints and reliability requirements with the need for an open-world assumption. Users increasing expectation for multimedia services is placing strong demands for the same to be available in MCS domains like air, rail and road transport. In the near future almost every consumer electronics device will be connected to an ecosystem for collecting and exchanging data, for example advance driving assistance, autonomous driving, etc.; and to provide services like payment systems, streamed content, etc. Experts estimate that the IoT market will consist of about 30 billion devices by 2020. Future MCS will be connected to cloud and other non-MCS systems, possibly from third-party vendors, where the trust is not very high. These systems are also called Open Distributed Real-time Embedded (ODRE) systems. Such MCS should not only consider safety but also security, esp. because there cannot be safety without security. For example, one of biggest threats faced by autonomous vehicles, an application domain of MCS, is vehicle cyber-security. One of the central challenges in vehicle security is that the various electrical components in a car (known as electronic control units, or ECUs) are connected via an internal network. Thus, if hackers manage to gain access to a vulnerable, peripheral ECU — for instance, a car's Bluetooth or infotainment system —, from there they may be able to take control of safety critical ECUs, like its brakes or engine, and cause catastrophic consequences.

Certification Authorities (CAs) demand the certification of MCS with strong confidence in the execution time bounds. As a consequence, CAs use conservative assumptions in the worst-case execution time (WCET) analysis which result in more pessimistic WCETs than the ones used by designers. Multicore and manycore systems, and open world assumptions add to the complexity of the MCS design and increase the certification cost, time and risks. Also, closed hardware design is making the certification of MCS more and more difficult. Furthermore, certification guidance from regulation authorities is still preliminary and not complete with respect to multicore systems.

Model-Driven Engineering (MDE) process enables to easily deploy applications onto a platform, and constitutes its interface to system designers and integrators. MDE can raise the level of abstraction in program specification and increase automation in program development in MCS.

These paradigm shift and upcoming trends have an impact on many aspects of MCS design. This

paper details several key challenges that need to be tackled in next five to ten years, in order to improve mixed criticality systems. It is based on the road mapping process that took place during the DREAMS project with inputs from project partners and the MCS community. It is to act like a guide to steer the research efforts by the MCS community.

# 1.5 Related Projects

There are some preliminary set of projects to build upon in the area of safety-critical systems. The objective of **Distributed REal-time Architecture for Mixed criticality Systems (DREAMS)** project was to develop a cross-domain architecture and design tools for networked complex systems where application subsystems of different criticality, executing on networked multi-core chips, are supported. DREAMS delivers architectural concepts, meta-models, virtualization technologies, model-driven development methods, tools, adaptation/reconfiguration strategies and validation, verification and certification methods for the seamless integration of mixed-criticality to establish security, safety and real-time performance. Some other projects related to DREAMS and MCS are as follows:

- Artemis CROSS Domain architecture (ACROSS) project realizes a cross-domain multi-core chip with the service architecture defined in the GENESYS project, including a FPGA-based multi-processor system on a chip implementation of a time-triggered network-on-chip (TT-NoC), tailored middleware components and flexible, embedded tools.

- Adaptivity and ConTrol Of Resources in embedded Systems (ACTORS) project addresses the challenging problem of efficient design of embedded systems for complex and demanding high-performance applications. The project approach is to raise the abstraction level of the specifications and computing models, to include resource-constrained design exploration stages and real-time resource adaptation by developing the appropriate models and tools supporting the design from the specification down to the embedded implementation.

- Automotive, Railway and Avionics Multicore Systems (ARAMIS) project goal is the improvement of the operational safety of automobiles, trains and airplanes. Timing, determinism, influence on safety, real-time applications and certification are the major fields of research.

- **CErtification of Real-Time Applications desIgNed for mixed criticaliTY (CERTAINTY)** project aims to push forward the certification of real-time mixed critical embedded systems, a process currently challenged by the choices made at application design time about reliability and disturbances handling, which deals with the management of interferences between different functions of complex control software over the whole system.

- Cost-Efficient Methods and Processes for SAfety-Relevant Embedded Systems (CESAR) project was started to provide improved methods, tools and demands for embedded systems development in domains of Aerospace, Automotive, Automation and Railways. CESAR addresses the entire system engineering life cycle by improving its disciplines and implementing fundamentals for interoperability in a reference technology platform (RTP) as an integrated tool platform.

- CRitical sYSTem engineering Acceleration (CRYSTAL) project project aims at improving the engineering process of embedded systems mainly by defining an Interoperability Specification (IOS) as a common backbone and means of integration among the various tools used in the design, engineering, implementation, testing and verification of embedded systems.

- Dynamic Variability in complex Adaptive systems (DiVA) project provides a new toolsupported methodology with an integrated framework for managing dynamic variability in adaptive systems. This is obtained by combining aspect-oriented and model-driven techniques in an innovative way.

- Framework for Real-time Embedded Systems based on COntRacts (FRESCOR) project is aimed at developing a framework that integrates advanced flexible scheduling techniques directly into the embedded systems design methodology, covering all the levels involved in the implementation, from the OS primitives, through the middleware, up to the application level.

- Multi-cores Partitioning for Trusted Embedded Systems (MultiPARTES) project is aimed at developing tools and solutions for building trusted embedded systems with mixed criticality components on multicore platforms.

- **Open VEhiculaR SEcurE platform (OVERSEE)** project aims to improve efficiency and safety of road transport by developing the OVERSEE platform, which aims to provide a secure, standardized and generic communication and application platform for vehicles.

- REduced Certification COsts Using Trusted Multi-core Platforms (RECOMP) project establishes methods, tools and platforms for enabling cost-efficient (re-)certification of safety critical and mixed criticality systems. Applications addressed are automotive, aerospace, industrial control systems, lifts and transportation systems.

- Safety Certification of Software-Intensive Systems with Reusable Components (SAFE-CER) project targets increased efficiency and reduced time-to-market by composable safety certification of safety-relevant embedded systems. The industrial domains targeted are within automotive, construction equipment, avionics, and rail.

- Scalable and reconfigurable electronics platforms and tools (SCARLETT) project implements the innovations in Distributed Modular Electronics (DME) concept to improve scalability, portability, adaptability, fault tolerance and reconfiguration capabilities in the current Integrated Modular Avionics (IMA1G).

- Trusted computing Engineering for Resource constrained Embedded Systems Application (TERESA) project defines, demonstrates and validates an engineering discipline for trust that is adapted to resource constrained embedded systems. Trust is defined as the degree with which security and dependability requirements are met.

- Timing Model TOols, algorithms, languages, methodology, USE cases (TIMMO-2-USE) project addresses a significantly increased automation for more predictable development cycles in order to substantially reduce development risks and time-to-market, and to increase reliability, safety, robustness, and fault tolerance by a much higher degree.

- TRustworthy Embedded systems for Secure Cloud Computing Applications (TRESCCA) aims to lay the foundations of a secure and trustable cloud platform by ensuring strong logical and physical security on the edge devices, using both hardware security and virtualization techniques while considering the whole cloud architecture.

- VARiability In safety-critical Embedded Systems (VARIES) project aims embedded system developers to maximize the full potential of variability in safety critical embedded systems. The

objectives of this project, with respect to safety critical embedded systems, are (1) to enable companies to make informed decisions on variability use in, (2) to provide effective variability architectures and approaches, and (3) to offer consistent, integrated and continuous variability management over the entire product life cycle.

- VERification-oriented and component-based model Driven Engineering for real-time embedded systems (VERDE) project aim is developing and industrialising a solution for iterative, incremental development and validation of real-time embedded systems in aerospace, software radio, railway and automotive domain.

- SW/HW extensions for virtualized heterogeneous multicore platforms (vlrtical) project aims the vertical and full development of the virtualization concept addressing the specific requirements for effective embedded virtualization. A virtualization-ready SoC platform and the associated programming models are developed, tackling all the system layers: applications, programming model, hypervisor and hardware.

- Probabilistic real-time control of mixed-criticality multicore and manycore systems (PROX-IMA) project provides industry ready software timing analysis using probabilistic analysis for manycore and multicore critical real-time embedded systems, and will enable cost-effective verification of software timing analysis including worst case execution time.

- **SAFEPOWER** project goal is to enable the development of low power mixed criticality systems through the provision of a reference architecture, platforms and tools to facilitate the development, testing, and validation of these kinds of systems according to the market needs

- Embedded Multi-Core systems for Mixed Criticality applications in dynamic and changeable real-time environments (EMC<sup>2</sup>) project finds solutions for dynamic adaptability in open systems, provides handling of mixed criticality applications under real-time conditions, scalability and utmost flexibility, full scale deployment and management of integrated tool chains, through the entire life cycle.

- Design of embedded mixed-criticality control systems under consideration of Extrafunctional properties (CONTREX) project's main challenge is to guarantee timing, power, temperature, and reliability requirements by controlling (shared) resource usage and access on the execution platform. It has also considered extra-functional constraints right from the beginning, represented extra-functional properties in executable prototypes and included these properties into local and global scheduling and control decisions.

- Open Platform for EvolutioNary Certification of Safety-critical Systems (OPENCOSS) project provides the first European-wide open safety certification platform: an Open Platform for Evolutionary Certification Of Safety-critical Systems for the railway, avionics and automotive markets.

- Safety And Security By Design For Interconnected Mixed-Critical Cyber-Physical Systems (SAFURE) project targets the design of cyber-physical systems by implementing a methodology that ensures safety and security "by construction".

## **1.6** Document Overview

Chapter 2 to 5 represent some of the key domains of application for  $\operatorname{MCS}$ :

- Ch.2 Avionics,

- Ch.3 Automotive In-Vehicle Networks,

- Ch.4 Windpower, and

- Ch.5 Healthcare.

Key research directions in MCS are represented by Chapter 6 to 12:

- Ch.6 Real-time Systems and Scheduling,

- Ch.7 Architecture,

- Ch.8 Security,

- Ch.9 Multi-core Chips,

- Ch.10 Operating Systems and Hypervisors,

- Ch.11 Certification, Safety and Dependability, and

- Ch.12 Modeling and Tooling.

Each chapter is divided in three main blocks: Key Research Challenges, Problems not solved in DREAMS and innovations need for the Roadmap to be achieved. State-of-the-art for each of the corresponding challenge is also mentioned.

# 2 Avionics

# 2.1 Research Challenges

#### C.1 Exploitation of multicores in safety critical systems

The avionics domain has been replacing complex, fragile and heavy mechanical circuits by software (electronic) solutions to reduce the inconvenient of the mechanical circuits. An example of such, is the fly-by-wire solutions introduced in the civil market with Airbus A320, replacing the mechanical flight controls by computers based solutions (typically called LRUs). Traditionally each functionality required in an aircraft required one or more LRUs, but an LRU wasn't used for more than one functionality. This is so called Federated Avionics Architecture approach. However, as the number of required functionalities increases, that is no longer a solution. An aircraft like the Airbus A380 would require more than 100 LRUs (130 approximately) to implement the required functionalities [Iti07]. For that reason the Integrated Modular Avionics (IMA) architecture was introduced [EUR01]. IMA allows to integrate multiple functions in a single LRU with a single core processor, while ensuring the spatial and temporal isolation requirements. With the usage of the IMA for the design of the Airbus A380, the number of LRUs used was limited to approximately 100 [Iti07]. However, new and smaller aircraft will require more computing power to allow further integration or the deployment of more complex functionalities.

To enable these new aircraft designs without increasing the number of LRUs (or maybe even reducing them) multi-core processors are a promising solution. However, while they provide the required performance increase necessary, the interferences between cores [NPB<sup>+</sup>14] hinders their usage in safety critical products, as planes. In order to satisfy the temporal isolation requirements new *deterministic platform software solutions* [GJLR<sup>+</sup>15] need to be provided, while enabling an efficient exploitation of the multi-core processors. DREAMS addresses this issue by developing a *regulation software* solution, a distributed run-time WCET controller enhanced with quality of service approaches [KPR<sup>+</sup>14]. The controller enables the concurrent execution of critical and non-critical applications in a multi-core, ensuring critical applications deadlines while maximizing the non-critical application, and if a situation of danger is observed the non-critical applications are stopped until the finalization of the critical application time window.

#### State-of-the-art

- S.1 The authors of [Fis14] propose a similar approach to the one proposed in DREAMS, however in [Fis14] during the execution of a critical application in one core all the other cores remain unused (or deactivated), so no concurrency is exploited when a critical application is executed. While that solution allows the deployment of critical and non-critical applications in a multi-core, the resources (the cores not used by the critical application) are not fully exploited.

- S.2 In [YYP<sup>+</sup>13a] the authors propose a similar system to the DREAMS controller. It uses memory bandwidths controllers exploiting the processor performance counters to control the memory usage of the applications using the system.

#### C.2 Fault-tolerance on distributed multi-core systems

In order to ensure the reliability of the system stringent development rules as those defined in the avionics standards like the DO-178 [EUR92] for software development or the DO-254 [EUR00] for hardware development. However, a single system can always suffer a hardware or software failure which which can put the system (i.e. aircraft) in a critical situation. Among others redundancy solutions have been introduced [HM01] to ensure the safety of the system on systems failure occurrence, like: triple modular redundancy (TMR), triplex redundancy, hybrid TMR arrangement, or triplex voter-comparator. These solutions considered systems with single-core, with multi-core processors new solutions can be envisioned to reconfigure the system while ensuring the system safety. For example, failures in a core of a multi-core doesn't mean that the system using the faulty core needs to be considered as faulty, if the multi-core contains other cores that can be used to allocate the safety critical functions in the system.

DREAMS addresses fault-tolerance on distributed systems using multicores with a resource management solution capable of detecting core failures at runtime and reconfigure the system  $[DFG^+16]$ . Core failure detection on a system (multi-core) is performed through a software monitoring service running on each core. On a core failure event, the system local resource manager is notified of the failure and a new schedule computed at design time is activated if possible (i.e. if the system has enough resources, cores, available to run the required functions). Moreover, in a distributed system, the system local resource manager reports its system status to a global resource manager, which can take global reconfiguration actions affecting multiple systems, to ensure that all the required functions (critical functions) are active.

To compute at design time the distributed system schedules in case of core-failure events a reconfiguration strategy and associated tool (GRec) is proposed. Reconfigurations graphs generated by GRec are used to configure the local resource managers and global resource manager to perform the reconfigurations at runtime.

#### State-of-the-art

- S.1 In the SCARLETT project [PBB<sup>+</sup>12] an approach similar to the one introduced in DREAMS is proposed, the main difference being the resource management services architecture and that the authors in [PBB<sup>+</sup>12] only consider single-core processors.

- S.2 The DIANA project [EJS<sup>+</sup>10] proposes a solution similar to those in DREAMS and SCAR-LETT [PBB<sup>+</sup>12]. While [PBB<sup>+</sup>12] proposes a centralized controller for the global reconfigurations, in [EJS<sup>+</sup>10] a decentralized controller is proposed. The approach proposed in DREAMS proposes a centralized controller, but at local level (a multi-core) reconfigurations can be done without being requested by the global resource manager.

### 2.1.1 Problems Not Solved in DREAMS

### $D.1\,$ Efficient integration of critical applications in multicores

With the above mentioned deadline-overrun technique, see Section 2.1 C.1, a critical application can be combined with non-critical applications running in parallel in a multi-core. Multiple critical applications can be integrated in the system, the deadline-overrun technique doesn't address the issue of how critical applications can be executed concurrently.

#### State-of-the-art

This issue has been addressed in other works:

- S.1 The authors in [DFG<sup>+</sup>14], [MNPGP16, MNN<sup>+</sup>17], and [TMW<sup>+</sup>17] propose to decompose critical applications tasks in three phases: the *acquisition* phase during which the task data is fetched from the main memory into a core local memory, the *execution* phase during which the task executes using only the local memory and the *restitution* phase during which task results. A simple, but stringent, constraint is put into schedules using this three phases task model: during the execution of a task *acquisition* or *restitution* phase no other cores can be executing other tasks *acquisition* or *restitution* phases. When following this approach, tasks (and thus applications) are ensured not to suffer interferences due to the usage of shared resources, as a single *acquisition* or *restitution* phase is ensured to use the shared resources at any moment.

- S.2 The PROARTIS [CQnV<sup>+</sup>13] and the PROXIMA [CAA<sup>+</sup>16] propose an alternative development and design methodology based on probabilistic methods. Thanks to these approach, statistical methods ensuring the safe combination of critical applications in a multi-core could be used. However, to enable the usage of such methods processors developed presenting specific time behavior (random) must be used, making it difficult to apply to COTS<sup>1</sup> processors.

- S.3 Agrawal et al. [AFF<sup>+</sup>17] propose a scheduling and runtime solution for systems similar to those studied in DREAMS (slot-based triggered-time systems) to allow the concurrent execution of critical tasks in a multi-core. Their solution is based on the definition of a scheduling taking into consideration the memory bandwidth requirements of the tasks executing in the processor. This even allows to assign the remaining bandwidth to non-critical tasks. A specialized runtime ensures that no task (specially non-critical tasks) uses more than the allocated bandwidth, stopping those tasks that have used the allocated bandwidth to avoid interferences not considered during the scheduling phase.

#### D.2 Application state and fault-tolerance on distributed multi-core systems

The DREAMS fault-tolerance mechanism implementation considers that the reconfigured applications are stateless or that can recover a state in the new configuration without compromising the system during the state recovering. However, state for non-stateless applications is completely lost on a reconfiguration between different nodes<sup>2</sup>.

#### State-of-the-art

- S.1 Redundancy (e.g., vote systems) solutions [HM01] provide this implicitly, as all the systems are always executing the application.

- S.2 While projects as SCARLETT [PBB<sup>+</sup>12] and DIANA [EJS<sup>+</sup>10] have addressed the fault-tolerance on distributed systems issue, as in DREAMS they seem to not have addressed the application state.

<sup>&</sup>lt;sup>1</sup>Component Off The Shelf

$<sup>^{2}</sup>$ If a reconfiguration moves an application from a core to another of a core the state is not lost, if both cores share the memory system.

## 2.2 Innovation for Roadmap

#### 1.1 Peripherals on mixed-critical systems

While the subject of using multicores for safety-critical systems is an ongoing topic, few to none have addressed the usage of peripherals on such systems. For an example, in an aircraft a large number of functions behavior depend on an important number of sensors and external information. This information is typically acquired by the processor using different mechanisms (i.e. other than the memory subsystem) than those studied by the current literature, like specialized interfaces. The usage of these interfaces in multi-core systems introduce new sources of interferences that should be addressed.

#### 1.2 Combination of regulation and control mechanisms

In the current literature a good number of regulation and control mechanisms [GJLR<sup>+</sup>15] have been introduced, as the deadline-overrun regulation mechanism introduced in DREAMS. Typically, regulation mechanisms address the combination critical applications with non-critical applications on multi-core processors, while control mechanisms address the combination of critical applications executed in parallel. The combination of both approaches could improve the utilization of the system and the performance of the applications running on it.

#### 1.3 Some other points regarding innovation for roadmap with respect to Avionics are:

- Fault-tolerance solutions and redundancy

- Design of safety critical heterogeneous systems (FPGA and specialized circuits)

- HW/SW systems for mixed-critical systems

- Interference quantification for multicores

# 3 Automotive In-Vehicle Networks

## 3.1 Research Challenges

# C.1 An increasing amount of functionalities, and each of them with increasing processing and/or bandwidth requirements

In the automotive domain, there are an ever-increasing demand for more powerful processing devices, and in-vehicle networks with higher bandwidths. In this chapter, the emphasis will be on the latter aspect.

The initial solutions for in-vehicle networks involved the bus-based communication. Such approaches have a straightforward support for the publisher-subscriber model, and several application specific standards emerged, such as CAN, LIN and FlexRay. The common benefit of all these approaches is the concept of predictable scheduling (e.g. via fixed priorities, time-division-multiple-access, slotted ring etc.). Routing the traffic across different networks can be done by intermediate gateways. However, these approaches have significant limitations, one of the most important ones being that they cannot cope with increasing bandwidth requirements of the automotive domain. Namely, all these approaches have an upper-bound on the transfer data rate (range between 100 kbit and 10 Mbit).

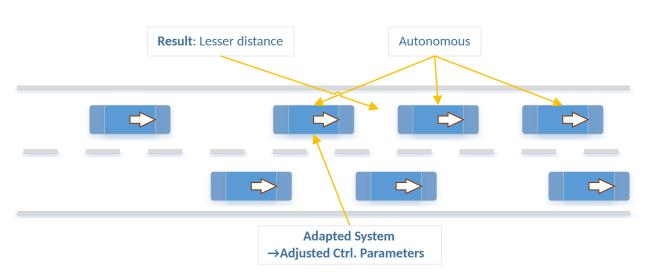

Future automotive systems are envisioned to have a vast number of very sophisticated functionalities, such as advanced driver-assistance systems, new generation of infotainment applications, and autonomous driving features. Implementing such functionalities within one system requires means to accommodate rapidly growing sensor traffic which can easily exceed the capacities of the aforementioned solutions (e.g. high resolution redundant image sensors). At the same time, such systems should also be able to accommodate complex low-latency traffic which is often of safety-critical nature.

**State-of-the-art** One viable solution to this problem is the switched Ethernet approach. The Ethernet networks are already well known in the domain of computer networks for their efficiency in terms of bandwidth. Their speed, at the present day, scales well with the growing technology demands (100Mbps  $\rightarrow$  1Gbps  $\rightarrow$  10Gbps  $\rightarrow$  ...). Another useful Ethernet characteristic is that it has open network capabilities, which is an important requirement for the open-world assumption. Finally, the Ethernet technology is widespread across other areas, such as avionics and industry, so there is already a substantial experience with using these networks, which can significantly accelerate the process of their integration into the automotive domain.

# C.2 Ethernet is envisioned as the backbone of the automotive network infrastructure. It is an imperative to employ data transfer strategies which are amenable to real-time analysis

As already explained, CAN, LIN and FlexRay networks cannot be efficiently employed for the entire in-vehicle network of next-generation automotive systems. Nonetheless, they are still very efficient when applied to small sub-networks. Therefore, the most promising approach for the future in-vehicle networks is to have Ethernet as the network backbone, which connects sub-networks

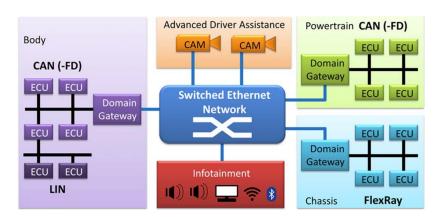

Figure 3.1: Example of in-vehicle network architecture

(CAN, LIN and FlexRay) into a unified system, where each of them presents the communication infrastructure dedicated to one functionality (e.g. powertrain, advanced driver assistance, infotainment). An example of this architecture is illustrated in Figure 3.1.

However, Ethernet was not designed with the real-time aspects in mind, and before it can be efficiently used in real-time systems, it is important to make it amenable to real-time analysis. The Time-Sensitive Networking (TSN) task group [tsn12] was founded with exactly that aim. This group works on a set of standards for time-sensitive traffic. One topic which attracts a lot of attention is the traffic shaping policy within network switches. The most well-known existing approaches are so called standard ethernet which includes static priority non-preemptive policy, and the AVB method, where traffic is, based on its criticality, classified into several categories which conform to different arbitration rules. In addition to that, the TSN group currently investigates several additional traffic shaping policies, such as Time-Aware Shaper, Burst-Limiting Shaper, Peristaltic Shaper, and Urgency-Based Scheduler. Moreover, the TSN group recently standardised the concept of frame preemptions [TSN16], which allows to achieve an ultra-low latency for high criticality frames.

As it is evident from the previous discussion, there are numerous ways and options to configure an Ethernet-based network. However, having more choices can is some cases be misleading, and usually presents an additional overhead when it comes to standards and inter-technology compatibility. Therefore, it is currently an imperative to perform a thorough and in-depth analysis and evaluation of existing techniques for real-time Ethernet, and proceed with the subset of the most promising ones. Additional aspects that need to be investigated are configurations of shapers (where applicable, e.g. AVB), topology selection, traffic classification and priority assignment (where applicable, e.g. standard Ethernet).

**State-of-the-art** The Ethernet technology has been extensively studied over the past several years. In this section, we will limit the discussion to the approaches related to real-time systems.

First, the formal analysis for the Ethernet standard (strict priority non-preemptive) and the AVB shaper was proposed [DTE12]. Then, the worst-case analysis method was proposed for the weighted round-robin arbitration mechanism [TDA<sup>+</sup>13]. The aforementioned worst-case analysis methods were gradually improved [ATED14, BAEP14, TAES14, TAE15, APB<sup>+</sup>17]. The worst-case analysis methods were also proposed for the later introduced Time-Aware Shaper and the

Peristaltic Shaper [TED15], as well as for the Burst-Limiting Shaper [TE16c] and the Urgency-Based Scheduler [SS16]. After that, the concept of frame preemptions was also analysed from the real-time perspective [TE16b]. Finally, the software-defined networking (SDN) concept for Ethernet was investigated [TE16a] as well as the gateway strategies for CAN-to-Ethernet networks [TSAE15].

#### C.3 Automotive in-vehicle network as a collection of sub-networks connected with the Ethernet backbone

With the envisioned automotive in-vehicle network architecture, where smaller sub-networks such as CAN, LIN and FlexRay are connected via an Ethernet backbone, one major challenge is to efficiently integrate all these technologies into a unique system. The most evident open question is how to organise the data transfer across different networks and how to configure the interfacing elements, often called gateways.

**State-of-the-art** As previously mentioned, the gateway strategies for CAN-to-Ethernet gateways have already been investigated [TSAE15], while gateways connecting other network types are likely to be studied in the near future.

#### C.4 Safety aspects of in-vehicle networks

Given that automotive domain falls into the category of real-time systems with numerous safety critical functionalities, it is an imperative to assure a high level of safety. The TSN group has proposed a proactive method towards transient transmission faults, which involves redundant paths. This approach has been standardised under the name 802.1CB - Frame Replication and Elimination for Reliability [TSN17a]. It allows to replicate the traffic within network elements and send it concurrently via redundant paths towards the same destination. It remains to be investigated how efficient this approach is, as well as are there many other techniques which can be used to mitigate the effects of transitional and/or permanent component/link failures. Finally, if it is possible to achieve a graceful degradation property and still meet some requirements when some of the system components experience a failure, remains an open question.

#### C.5 Security aspects of in-vehicle networks

Similar to the safety aspect, the automotive systems require a high degree of security. This aspect becomes more important and emphasised with the open-world assumption, where an extensive interaction of the system itself with the outside world is expected. At the same time, the increasing complexity of automotive systems implies that the same manufacturer cannot produce all functionalities, but instead some of them must be acquired from different suppliers. This raises a question whether all components of the system can be fully trusted, and also infers that the security aspects need to be addressed not only concerning the outside world, but also concerning the functionalities within the system itself. The TSN group proposed an approach based on stream filtering [TSN17b], which allows to prevent a network saturation. It remains to be investigated whether this approach is efficient, as well as are there some other security mechanisms that can also be applied. Finally, can Software-Defined-Networking (SDN) principles be used to enhance the system security is a valid research question.

# 3.2 Innovation for Road-map

# 1.1 The mix of different sub-networks of different type and purpose into a unique heterogeneous network system

The future automotive in-vehicle network is envisioned to be an heterogeneous system with small sub-networks based on CAN, LIN and FlexRay technology, connected via gateways to an Ethernet network backbone. The network topology and the configuration would be such that low latencies can be guaranteed for the high-critical traffic, and at the same time the best-effort service will be provided for functionalities that have significant bandwidth requirements. The configuration of network elements which represent the interface between different sub-networks (i.e. gateways) should be use-case dependent and heavily optimised for the given traffic, in order to provide the desired behaviour.

# 1.2 SDN is likely to be used in in-vehicle networks, and it will provide the means to implement safety and security features

The SDN functionality is likely to be used in the next generation of in-vehicle networks. Its concepts and application are well understood in different application domains, so the integration of SDN services into the automotive domain is expected to be relatively quick. Having a centralised monitoring entity offers lots of possibilities and efficient means to implement various safety- and security-related features. Given that enhancing safety and security are among the most important milestones in the development process of the future generation automotive vehicles, it is foreseen that advanced SDN systems are likely to be used to aid in that cause.

# 4 Wind Power

## 4.1 Research Challenges

#### C.1 Increase system reliability and maintainability

A modern off-shore wind turbine dependable control-system manages up to three thousand inputs and outputs, several hundreds of functions are distributed over several hundred nodes grouped into eight subsystems interconnected with a field-bus and the distributed software contains several hundred thousand lines of code [PGN<sup>+</sup>14a, PGN<sup>+</sup>14b].

The complexity of those systems challenges several dependability properties such as safety, availability, reliability and maintainability. The integration of additional functionalities also leads to an increase in the number of subsystems, connectors and wires increasing the overall cost-size-weight and reducing the overall reliability of the system. For example, based on domain specific field data from other domains it is considered that between 30-60% of electrical failures are attributed to connector problems [PGN+14a, SM99].

Therefore the achievement of the maximum probability that a system provides the specified service until a time, given that the system was operational at the beginning, is hampered by the high number of subsystems and networks. In the same vein, the complexity of such systems affect to the time interval required to repair them after the occurrence of a benign failure due to the high fault-potential amount of subsystems.

#### State-of-the-art

- S.1 European research project MultiPARTES [MUL14] aimed to support mixed-criticality integrated architectures based on multicore and partitioning (e.g., hypervisor). This integration can increase system reliability by reducing the number of subsystems and associated wires and connectors [PGN<sup>+</sup>14a, PGN<sup>+</sup>14b].

- S.2 As the usage of fans for device thermal dissipation is not considered due to poor reliability characteristics, thermal analysis and management becomes relevant for the development of next generation control platforms, in order to support the integration of multiple mixed-criticality functions in multicore devices [PGN+14a, PGN+14b]. CONTREX aims to enable energy efficient and cost aware design through analysis and optimization of real-time, power, temperature and reliability with regard to application demands at different criticality levels [CON14]. SAFEPOWER aims to enable the development of cross-domain mixed-criticality systems with low power, safety and security requirements [SAF17a].

- S.3 EMC2 project's role is to explore the mechanisms for improving reliability on time transfer for industrial applications with a focus on the Smart-Grid market [EMC14].

#### C.2 Integrated architectures

The soaring demand for high performance and enhancing of the number of functionalities executed in today's embedded systems leads to the trend of moving towards integrated architectures [Ham03]. System engineers aim at the integration of multiple functionalities with different criticality regarding safety, security and real-time on the same embedded computing platform. These systems are usually referred to as mixed-criticality systems [BBBT11, PGN<sup>+</sup>14a, PGN<sup>+</sup>14b].

#### C.3 Single-core to multi-core transition

Single-core processors were used in the last decades and are used nowadays to develop mixedcriticality systems. Partitioned single-core processors were implemented in different domains such as lift, automotive, wind power for developing safety-critical systems. Partitioning is achieved using virtualization solutions such as hypervisors, which allow dividing the processing core into smaller parts (partitions) with local and shared memory and exclusive access to peripherals. However, the needs of the industry advance fast, and the amount of the data required to be transferred gets bigger and bigger. Those requirements limit the applicability of single-core processors such as their available resources are limited and are not scalable. Therefore, faster and more capable processors are required to accomplish the market request.

Multi-core and many-core processors are the natural transitions of single-core processors such as they provide high-performance capabilities that increase due to microarchitecture advances. Those processors provide benefits in terms of lower power consumption, which according to Pollack's law, it is linearly proportional to the increase in complexity, and lower size-weight-cost. They also provide better scalability, availability, maintainability and reliability.

#### C.4 Be able to meet safety, security and real-time

Mixed-criticality systems allow implementing applications with different criticality levels such as real-time, safety and security into the same system. Therefore, those systems should be able to meet criticality-related constraints such as time independence, spatial independence, diagnosis. For instance, a non-safety partition could access to the memory region of a safety partition and modify the data, or it could affect the temporal behaviour of the safety partition, taking too high a share of the available processor execution time.

In addition to this we should consider that nowadays and in the future: 'there is no safety without security' [Per17].

### C.5 Attest multi-core computing systems

Multi-core devices are prompt to interference due to resource sharing (memory, peripherals, processor time) and the communication between the elements necessary to achieve the overall goal design (partitions). Those issues challenge the attestation of systems based on a multi-core processor.

IEC 61508 Annex F recommends a set of "Techniques for achieving non-interference between software elements on a single-computer" [IEC10c]. However, those techniques are not at all applicable in multi-core devices, such as one resource can be shared among the elements of the system. Therefore, the need for new or extended measures and diagnosis techniques is identified in this project.

### C.6 Attest product families

A product line is a range of similar products that are developed by the same company. Individual products in such a product family are similar, but still slightly different. The current state of the art is to attest individual systems, where if safety, security or real-time aspect changes, the entire system should be re-certified. There are, however, attempts to achieve incremental certification

where only those parts that need recertification are reassessed when a product is enhanced or comes with a new version. This task goes one step beyond incremental certification into modular and product-line certification.

#### State-of-the-art

S.1 In OPENCOSS research project a model based assurance of safety-critical product lines is defined [KHM $^+16$ ].

#### C.7 Integrate model driven engineering

Model-driven engineering (MDE) focuses on creating and exploiting domain models, representing the knowledge and activities of a particular application domain. MDE can be integrated with safety life cycles (e.g., IEC 61508) in order to increase the development efficiency, cost reduction and reduce the probability of human systematic errors.

#### State-of-the-art

S.1 OPENCOSS research project integrates the goal structuring notation (GSN) MDE to represent safety cases [OPE14].

#### C.8 State of the art and next generation SoC

The number of transistors in the integrated circuits doubles proximately every two years. This observation entails the increase of the capabilities and complexity, which impacts on the development and certification cost of next-generation system-on-chips (SoC). The performance of those systems increases due to microarchitecture advances. The performance is roughly proportional to the square of the increased complexity.

Moreover, reducing the on-chip power consumption has become a key challenge in SoC domain. The continuing trend for ever increasing functionality, performance, and integration within SoCs is leading to designs with power issues (dissipation). These systems require expensive packaging, heat sinks, and a cooling environment, which lead to additional matters related to the availability and maintainability of future developments.

#### C.9 Integration of programming paradigms

Modern off-shore wind turbine dependable control-system manages several hundreds of functions which are distributed over several hundred nodes grouped into different subsystems interconnected with a field-bus and the distributed software that contains several hundred thousand lines of code [PGN+14a, PGN+14b]. Those systems allow to integrate different programming paradigms (e.g., C, C++, HDL) as they enable to integrate processing systems and programmable logic into the same system architecture.

#### C.10 Digitalization of the wind turbine

Digitalization has revolutionized the proprietary infrastructure and the control and management of dependable embedded systems. Patent documents can now be obtained in a digital version. Physical records are being digitalized to ease the access. Furthermore, digitalization enables the remote control of systems such as wind-turbines, monitoring and controlling their behaviour and reacting to any discrepancies detected. Nevertheless, the digitalization has associated risk factors, such as security. The security threat potential in the digital era needs to shift from securing network perimeters from safeguarding data propagated across systems, devices, and the cloud.

This challenge needs to consider the integration and evolution of IIoT, e.g., QoS communication with cloud infrastructure, cloud computing, delocalization of some real-time and safety partitions, cybersecurity.

### 4.1.1 Problems Not Solved in DREAMS

#### D.1 Support real-time, safety and security

The wind turbine system defined in European project DREAMS focuses on safety and real-time. Security was not considered in the case study definition.

#### D.2 Attest multi-core mixed-criticality systems

Although in DREAMS we develop a set of generic and reusable patterns applicable to hypervisors, COTS multi-core devices and mixed-criticality networks, further solutions could be generated to tackle the remaining issues detected in  $[LAO^{+}16, LMB^{+}17]$ .

#### D.3 Attest wind turbine product families

In DREAMS we generate a safety argumentation scheme for IEC 61508 compliant system, which aims to decrease the cost and time required for developing and certifying a wind turbine. This scheme defines the safety-related arguments of a wind turbine and the evidences that support those arguments. However, the implementation of the argumentation system has not been validated in an industrial safety project or formal certification assessment.

### 4.2 Innovation for Road-map

#### 1.1 Product family modular safety argumentation scheme

The attestation of a product family is an expensive and time-consuming process analysed in some research projects (e.g., OPENCOSS). DREAMS research project contributes a generic and reusable modular IEC 61508 compliant safety-argumentation scheme based on a wind turbine product family. Also, this argumentation scheme supports variation points from standards. It supports safety-domain-specific standards such as it is based on IEC 61508, which is the main standard for E/E/PE functional safety, and security and real-time standards such as it was generated to support further domain criteria (e.g., ISO 26262, ISO 13849). In addition, it supports variation points from requirements. The modification of one requirement of one of the components that compose the product line does not affect the overall design as it is defined considering modularity methodology. Modularity enables the subdivision of a system into smaller parts (modules), which can be independently generated and certified.

#### $1.2 \ \ \textbf{Generic and reusable cross-domain mixed-criticality patterns}$

In this project, we analyse the IEC 61508 safety standard, and we identify some improvements regarding the techniques applicable to partitioned and networked multi-core systems. As the result of that analysis we define, implement and generate a set of generic and reusable patterns to solve remarkable issues of those systems.

#### 1.3 Multicore / Manycore with virtualization for the development of next generation highcomputing mixed-criticality solutions for for Wind Turbines

Innovation roadmap already described in Sections 2, 3 and 9.

#### 1.4 Wind Turbine digitalization and Industry 4.0

The digitalization of wind-turbines with the integration and evolution of Industrial Internet Of Things (IIoT), opens a new innovation path between the integrated architectures to be deployed in the wind turbine and the external cloud architecture to be deployed integrating technical challenges such as QoS communication with cloud infrastructure, cloud computing, delocalization of some real-time and safety partitions and cybersecurity.

# 5 Healthcare

## 5.1 Research Challenges

#### C.1 Real-Time ECG Monitoring

Prolonged real-time ECG monitoring is needed for improved detection of diseases. Most industrial products, e.g. AliveCor, BodyGuardian, LifeMonitot, NowCardio, and PhysioMem, capture, process and transmit ECG data to a server for offline analysis by specialists. In addition, research on wearable monitoring and arrhythmia diagnosis concentrates on detection capability and focuses on Android and IoS smart apps. Android smartphone is often used to capture, analyze and visualize ECG for alerting the patient wearing the device in real time (but not the doctor).

**State-of-the-art** Transmission of ECG signals to a remote monitoring center for offline processing by medical personnel has been previously considered, with very limited work on hard and soft real-time communication. In respect to soft real-time, there are limited results on a) ECG data packetization and selection of TCP parameters during network transmission and b) on-the-fly ECG signal analysis and visualization of annotated patient data for real-time monitoring by physicians or clinicians. These aspects, treated in DREAMS, make our research on soft real-time ECG processing innovative.

### 5.1.1 Problems Not Solved in DREAMS

In DREAMS, we have evaluated real-time performance of ECG analysis for detecting non-fatal arrhythmias and visualization versus non-critical video processing when memory and network bandwidth regulation techniques are in place using both in-hospital (Linux-based), and out-of hospital (smartphone Android-based) scenarios based on a mobile wearable cardiac pulse sensor (ST Bodygateway). Although results are encouraging, the parameter space has not been fully explored in respect to memory, network and CPU bandwidth requirements and limits. Other issues relate to the support of the Bluetooth protocol on open source RTOSes for embedded systems, e.g. FreeRTOS. These issues affect system predictability of mixed criticality real-time embedded systems (inside and outside the hospital) supporting on-the-fly ECG analysis and visualization together with other applications (e.g. on a hospital media server), such as video decoding or streaming.

# 5.2 Innovation for Road-map

Extensions to supporting full diagnosis of different types of arrhythmias, with online monitoring of other important physiological data (heart rate, respiration rate, physical activity level and body position) ondemand in real-time is interesting. This requires additional paths, either from Doctor App to Patient App to program the BGW to send other biometric data (e.g. respiration or accelerometer), or from Cloud server to Patient App to allow patients to monitor their own heart rate in real-time, informing them and physicians to adjust medication, or call emergency services in case of a significant cardiac event.

# 6 Real-time Systems and Scheduling

## 6.1 Research Challenges

#### C.1 Quantifying timing interferences of shared resources in multicore systems

The use of multicore systems is rapidly increasing as execution platforms for real-time embedded systems because of their better performance/energy ratio, reduce infrastructure costs, and ease of management. Also, The field of embedded systems in experiencing a trend towards integrating multiple applications on a single multicore platform. However, the interference in shared resources in multicore platforms like caches, shared buses, memories, etc., poses several problems, and it is yet to see widely adopted commercial solution. It may severely reduce the performance of tasks executed on the cores, and increases the complexity of timing analysis and/or decreases the precision of its results.

The issue of timing analysis on multicore platforms is because of interference delays as a result of conflicting simultaneous access to the shared resources. These issues were not present in single core systems, or not at the same scale. For example, the latency of a memory access in single core depended only on the type of memory being accessed and whether it was cached or not. But in case of multicore, the latency of a memory access also depends on whether the same memory region is being accessed by other cores or not, as multiple simultaneous access may lead to contention; only one request can be served at a time, while others have to wait. The authors in [NPB<sup>+</sup>14], for example, demonstrated that the latency of a single memory store operation can increase by a factor of 25.82 in a Freescale P4080 multicore platform when the number of active cores increases for 1 to 8. Thus the determination of worst-case execution time is complex, and the estimation is much higher than the observed average/best-case. Methods for scheduling tasks and resource access that help in reducing pessimism of WCET analysis are required.

**State-of-the-art** Many techniques use Time-Division Multiple Access (TDMA) like arbitration mechanism where resource access is provided to tasks in statically assigned time slices. These techniques provide high predictability, but yield poor resource utilization since unused slices are wasted [KHMF13]. For example, Schranzhofer *et al.* [SPC $^+$ 11] divide the task execution in phases, and tasks are only allowed to access shared resources in certain phase while making sure no other task are simultaneously in resource access phase. Bonal et al. [BCNP12], divide the task execution in sub-tasks and sub-tasks further in execution and communication slices. Shared resources access is only allowed in a communication slice. Some solutions involve using custom hardware like the predictable DRAM controller [VY15]; but it is not commercially viable to implement in hardware for a small market segment corresponding to real-time systems. Thus, restricting use of Commercial Off The Shelf (COTS) multicore platforms. Joint analysis methods like those consider by Chattopadhyay et al.  $[CKR^+12]$  are also popular, but have large computational complexity as they analyze the program flow on all cores considering shared resources. Several approaches, for instance [NPB<sup>+</sup>14], propose resources reallocation based on information derived from monitoring the utilization, e.g. the memory accesses. Agrawal et al.  $[AFF^+17]$  and similar works consider interference sensitive WCET (is-WCET), that computes offline the execution time of applications considering the memory access from applications that can execute in parallel.

#### C.2 Simultaneous execution of mixed-criticality applications on multicores of a single platform

The trend of multicore system also applies to safety critical domains, like Avionics and Automotive, where applications of several criticality levels execute on a single multicore platform. These criticality levels express the required protection against failure for the corresponding applications and system. For example, in case of Avionics, these criticality levels are also know as Development Assurance Level (DAL), and they are needed to be followed for certification. To execute such mixed criticality applications on a single multicore requires strict temporal and spatial isolation. Achieving this isolation is not that straight forward in multicore systems, esp. because many shared resources are required for performance and cost efficiency. Also, if applications of different criticality levels are allowed to access the shared memory in a random manner, then an application of lower criticality accessing a shared resource can block the access of any high criticality task that is executing in parallel. This can severely effect the response time of the high criticality applications. It is also difficult to quantify the impact on response time because of limited knowledge about the behavior of low criticality applications and some hardware resources like the shared-bus.

**State-of-the-art** As an initial step, safety-critical single-core avionics applications are ported to a multicore by preserving the original schedule as well as the source code while executing it on only one core. Historically, safety-critical real-time systems have been implemented using a cyclic executive (CE). This approach has been extended for multicore platforms by Burns *et al.* [BFB15]; the execution is coordinated on all cores so that the frames are released at the same time, and only applications of same criticality are allowed to execute concurrently. In DREAMS, we propose running a high-criticality task in parallel to low-criticality tasks on a multicore platform by using DREAMS resource management services (RMS); the execution of low critical task(s) is suspended on detection of a possible deadline overrun by the DREAMS RMS monitor. We further propose techniques to improve the system usage and performance of the low critical applications by using quality of service management schemes [DFG<sup>+</sup>16].

#### C.3 Incremental system extensions

Modern systems constantly need to update and upgrade in order to provide more features and to fix problems with the previous selves. For safety critical systems though, upon an update of a part of the system, the complete system needs to be verified & validated [ENNT15] (or certified) as per safety standards (IEC26262, for instance) in order to guarantee correct operation after deployment. If a system is designed without considering potential future extensions/modifications, the cost and efforts for certification of the system might prevent its deployment for the application. On the contrary, when the potential extensions are envisioned during the design phase of the system, only a number of modified sub-systems and the overall system functioning need to be certified [ENNT15].

To enable future extensions/modifications, the design and scheduling tools need to allow modification in the design without modifying the existing functionality. There exist a number of tool design approaches which intrinsically support such functionality by freezing the existing design and using the left-over resources. However, other approaches might not be as flexible for changes. In other words, the selection of the tool design approach affects the possibility for future extensions.

**State-of-the-art** The Xoncrete tool in the DREAMS tool-chain supports incremental scheduling by freezing a partition or a set of tasks and utilizing the left-over resources to schedule new tasks.

Similarly, a modification in a partition can be made without affecting the rest of the partitions (thanks to ARINC style partitions). Another approach was proposed by  $_iGA_i$  et al. [?] using compositional scheduling framework, however this approach might lead to potential bandwidth loss as mentioned by Lackorzynski et al. [LWVH12].

Note that, other than the inter- and intra-partition schedule, a re-configuration of other artifacts (e.g. on- and off-chip network schedule, virtual links, ports, modes of operation, etc.) might also be required upon an update. Although other tools in the DREAMS tool-chain do not support incremental development of a system [BDM<sup>+</sup>17b], but due to the flexible design of DREAMS meta-models and tool-chain such a feature can be added with minor efforts [BDM<sup>+</sup>17b].

#### C.4 Safety and Security-aware scheduling

In the past, these real-time systems were mainly concerned by safety and reliability requirements as they were physically isolated and ran on dedicated hardware. But many safety critical systems nowadays are networked or distributed and are moving towards a open-world assumption. For example, the trend of Internet of things (IoT) is coming to automotive systems; passenger comfort and infotainment features continue to progress through the advancement of in-vehicle networks and connectivity of the automotive system with its environment. These systems can no longer be bounded by static system structures but need to take into account components entering and leaving at runtime. The challenge here is not only to consider distributed and networked real-time systems, but also allow dynamic system structures and open world assumptions without compromising safety and reliability requirements of the systems.

In addition, these systems have also become an promising target for active and passive attackers. In the worst case, compromising a few components can bring down the entire system. An important challenge is ensuring the continuous unmaintained real-time operation of the system while guaranteeing safety and reliability requirements.

**State-of-the-art** In DREAMS project, we developed mechanism for detecting core failure, and provide fault-tolerance via reconfiguration in distributed system by using DREAMS RMS services[DFG<sup>+</sup>16]. In case of a core failure in multicore systems, critical applications are locally reconfigured in order of priority. Remaining applications that cannot be schedule, are reconfigured on another multicore platform of the distributed system if possible. During the DREAMS project, we developed security mechanisms to ensure the security of systems RMS communication as it handles critical system information and scheduling of tasks in the distributed DREAMS system [GKGP<sup>+</sup>16] [KGP<sup>+</sup>16]. Four different security levels are proposed which can be used as per the security requirement of the individual RMS communication channel. The same security mechanisms can also be used by applications that need secure communication.

Until recently security was an afterthought in the design of real-time systems. Most existing realtime systems don't consider security issues. Some works consider timing inference based security attacks as real-time systems, esp. Time-triggered systems that execute the same schedule, are vulnerable to them due to their inherent predictable nature. Krüger *et al.* [KVF17] propose an online mechanism to obfuscate the schedule through randomization while ensuring deadlines are met.

It is fairly well understood that the use of shared resources in a platform can lead to information leakage without the need for explicit communication between tasks. Mohan *et al.* [MYPB14] propose method to prevent information leakage through scheduling constraints and cleaning states

of shared resource, e.g.: flushing caches between runs of applications with different security requirements. These methods consider simplistic threat model and impose large number of constraints. In addition, cleaning up states of shared resources like cache can severely impact performance of the system. Pellizzoni *et al.* [PPY<sup>+</sup>15] also present a model for preventing information leakage in hard real-time systems showing how to capture security constraints as relationships between tasks and a new vendor oriented security model for information leakage.

## 6.1.1 Problems Not Solved in DREAMS

#### D.1 WCET and Scheduling Interdependence

The cyclic dependency between WCET and scheduling makes it difficult to define a feasible schedule.

**State-of-the-art** Groesbrink *et al.* [GAdSP14] propose single-Core equivalent virtual machines to make WCET independent of scheduling. [RNH<sup>+</sup>16] proposes co-estimation of WCET and schedule by modeling cache behavior, and accounting it in the schedule.

#### D.2 Running critical applications simultaneously in multicore systems