# Distributed REal-time Architecture for Mixed criticality Systems

# Initial Collection of Offline Adaptation Strategies for Mixed Criticality D 4.1.1

| Project Acronym     | DREAMS              | Grant Agreement<br>Number |           | FP7-ICT-2013.3.4-610640                  |       |

|---------------------|---------------------|---------------------------|-----------|------------------------------------------|-------|

| Document<br>Version | 1.0                 | Date                      | 2014-7-31 | Deliverable No.                          | 4.1.1 |

| Contact Person      | Ankit Agrawal       | 0                         |           | Technische Universität<br>Kaiserslautern |       |

| Phone               | +49 (0)631 205 3674 | E-Mail                    |           | agrawal@eit.uni-kl.de                    |       |

# Contributors

| Name                   | Partner |

|------------------------|---------|

| Ankit Agrawal          | TUKL    |

| Gerhard Fohler         | TUKL    |

| Ramon Serna Oliver     | ттт     |

| Silviu S. Craciunas    | ттт     |

| Øystein Haugen         | SINTEF  |

| Franck Chauvel         | SINTEF  |

| Simon Barner           | FORTISS |

| Claire Pagetti         | ONERA   |

| Patricia Balbastre     | UPV     |

| Fernando Eizaguirre    | IKL     |

| Jörn Migge             | RTaW    |

| Lionel Havet           | RTaW    |

| Zaher Owda             | USIEGEN |

| Mohammad Abuteir       | USIEGEN |

| Lionel Havet           | RTaW    |

| Alexander Mark Diewald | FORTISS |

# Table of Contents

| Сс | ontribut              | tors                                                                                      | 2  |  |  |

|----|-----------------------|-------------------------------------------------------------------------------------------|----|--|--|

| Li | List of Abbreviations |                                                                                           |    |  |  |

| 1  | Intro                 | oduction                                                                                  | 10 |  |  |

|    | 1.1                   | Objectives of this Deliverable                                                            | 10 |  |  |

|    | 1.2                   | Positioning of the Deliverable in the Project                                             | 10 |  |  |

|    | 1.3                   | Organization of the Deliverable                                                           | 11 |  |  |

| 2  | Over                  | rview of the Model Driven Development Process                                             | 13 |  |  |

|    | 2.1                   | Introduction                                                                              | 13 |  |  |

|    | 2.2                   | Models                                                                                    | 14 |  |  |

| 3  | Term                  | ninology/Definitions                                                                      | 16 |  |  |

|    | 3.1                   | Newly Defined Terms                                                                       | 16 |  |  |

|    | 3.1.1                 | 1 Aperiodic Task                                                                          | 16 |  |  |

|    | 3.1.2                 | 2 Application-specific Constraints                                                        | 16 |  |  |

|    | 3.1.3                 | 3 End-to End Flow (ETEF)                                                                  | 16 |  |  |

|    | 3.1.4                 | 4 End-to-End Latency                                                                      | 16 |  |  |

|    | 3.1.5                 | 5 Fault Model                                                                             | 16 |  |  |

|    | 3.1.6                 | 6 Mapping                                                                                 | 16 |  |  |

|    | 3.1.7                 | 7 Mode                                                                                    | 16 |  |  |

|    | 3.1.8                 | 8 Mode-change                                                                             | 16 |  |  |

|    | 3.1.9                 | 9 Partition Scheduling Plan                                                               | 16 |  |  |

|    | 3.1.1                 | 10 Partition Slot                                                                         | 16 |  |  |

|    | 3.1.1                 | 11 Periodic Task                                                                          | 16 |  |  |

|    | 3.1.1                 | 12 Restartable Task                                                                       | 17 |  |  |

|    | 3.1.1                 | 13 Schedule Reconstruction                                                                | 17 |  |  |

|    | 3.1.1                 | 14 Scheduling                                                                             | 17 |  |  |

|    | 3.1.1                 | 15 TT Scheduling Table                                                                    | 17 |  |  |

|    | 3.1.1                 | 16 Single Event Upset (SEU)                                                               | 17 |  |  |

|    | 3.1.1                 | 17 Sporadic Task                                                                          | 17 |  |  |

|    | 3.1.1                 | 18 Task                                                                                   | 17 |  |  |

|    | 3.1.1                 | 19 TT Slot                                                                                | 17 |  |  |

|    | 3.2<br>Princip        | Terms Defined in D1.1.1 - Architecture Conceptualization: Requirements, Terms and<br>oles | 17 |  |  |

|    | 3.2.1                 | 1 Assurance Level                                                                         | 17 |  |  |

|    | 3.2.2                 | 2 Error                                                                                   | 17 |  |  |

|    | 3.2.3                 | 3 Failure                                                                                 | 17 |  |  |

|    | 3.2.4                 | 4 Fail-operational System                                                                 |    |  |  |

| 3.2.6<br>3.2.7<br>3.2.8 | Fault<br>Fault-Containment Region                                                                                                                                                                                                                                                                                                                                                                                      |                                    |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| 3.2.8                   | -                                                                                                                                                                                                                                                                                                                                                                                                                      |                                    |

|                         | - 1                                                                                                                                                                                                                                                                                                                                                                                                                    |                                    |

|                         | Fault Hypothesis                                                                                                                                                                                                                                                                                                                                                                                                       | 18                                 |

| 3.2.9                   | Latency Constraint                                                                                                                                                                                                                                                                                                                                                                                                     | 18                                 |

| 3.2.10                  | ) Mixed-Criticality Systems                                                                                                                                                                                                                                                                                                                                                                                            |                                    |

| 3.2.12                  | Partition                                                                                                                                                                                                                                                                                                                                                                                                              |                                    |

| 3.2.12                  | 2 Repetition Constraint                                                                                                                                                                                                                                                                                                                                                                                                |                                    |

| 3.2.13                  | 3 Spatial Partitioning                                                                                                                                                                                                                                                                                                                                                                                                 | 19                                 |

| 3.2.14                  | Synchronization Constraint                                                                                                                                                                                                                                                                                                                                                                                             | 19                                 |

| 3.2.15                  | 5 Temporal Partitioning                                                                                                                                                                                                                                                                                                                                                                                                | 19                                 |

| 3.2.16                  | 5 Timing Constraint                                                                                                                                                                                                                                                                                                                                                                                                    | 19                                 |

| 3.2.17                  | Worst Case Execution Time (WCET)                                                                                                                                                                                                                                                                                                                                                                                       | 19                                 |

| 3.2.18                  | 3 Worst Case Response Time (WCRT)                                                                                                                                                                                                                                                                                                                                                                                      | 19                                 |

| 3.3 F                   | References                                                                                                                                                                                                                                                                                                                                                                                                             | 19                                 |

| Hiera                   | rchical Scheduling Algorithms                                                                                                                                                                                                                                                                                                                                                                                          | 20                                 |

| 4.1 (                   | Dverview                                                                                                                                                                                                                                                                                                                                                                                                               | 20                                 |

| 4.2 H                   | lierarchical Scheduling in Partitioned Systems                                                                                                                                                                                                                                                                                                                                                                         | 20                                 |

| 4.2.1                   | Hypervisor Scheduling                                                                                                                                                                                                                                                                                                                                                                                                  | 21                                 |

| 4.2.2                   | Partition Scheduling                                                                                                                                                                                                                                                                                                                                                                                                   | 22                                 |

| 4.3 (                   | Considerations of Static versus Priority-based Scheduling for the Hypervisor                                                                                                                                                                                                                                                                                                                                           | 23                                 |

| 4.3.1                   | Mixed Criticality                                                                                                                                                                                                                                                                                                                                                                                                      | 23                                 |

| 4.3.2                   | Certification                                                                                                                                                                                                                                                                                                                                                                                                          | 24                                 |

| 4.3.3                   | Incremental Certification                                                                                                                                                                                                                                                                                                                                                                                              | 24                                 |

| 4.4 (                   | Computational Model in Partitioned Systems                                                                                                                                                                                                                                                                                                                                                                             | 25                                 |

| 4.4.1                   | Tasks, Partitions, Execution flows                                                                                                                                                                                                                                                                                                                                                                                     | 25                                 |

| 4.5 1                   | echniques for Static Schedule Generation                                                                                                                                                                                                                                                                                                                                                                               | 27                                 |

| 4.5.1                   | Approaches                                                                                                                                                                                                                                                                                                                                                                                                             | 27                                 |

| 4.5.2                   | MAF Optimization                                                                                                                                                                                                                                                                                                                                                                                                       | 29                                 |

| 4.5.3                   | Jitter minimization                                                                                                                                                                                                                                                                                                                                                                                                    | 29                                 |

| 4.6 9                   | Scheduling in Multicore Systems                                                                                                                                                                                                                                                                                                                                                                                        |                                    |

| 4.6.1                   | Overview                                                                                                                                                                                                                                                                                                                                                                                                               |                                    |

| 4.6.2                   | Partitioned Systems                                                                                                                                                                                                                                                                                                                                                                                                    |                                    |

| 4.6.3                   | Global Systems                                                                                                                                                                                                                                                                                                                                                                                                         |                                    |

| 4.6.4                   | Scheduling Policies                                                                                                                                                                                                                                                                                                                                                                                                    |                                    |

| 4.7 ľ                   | Aultiple Execution Plan Generation                                                                                                                                                                                                                                                                                                                                                                                     | 33                                 |

| 4.8 I                   | ncremental Scheduling Generation                                                                                                                                                                                                                                                                                                                                                                                       | 33                                 |

| 4.8.1                   | Related Work                                                                                                                                                                                                                                                                                                                                                                                                           | 34                                 |

|                         | 3.2.10<br>3.2.12<br>3.2.12<br>3.2.12<br>3.2.12<br>3.2.12<br>3.2.16<br>3.2.17<br>3.2.16<br>3.2.17<br>3.2.17<br>3.2.18<br>3.2.17<br>3.2.18<br>4.1 0<br>4.2.1<br>4.2.1<br>4.2.1<br>4.2.1<br>4.2.1<br>4.2.1<br>4.2.1<br>4.2.1<br>4.2.1<br>4.2.1<br>4.2.1<br>4.3.2<br>4.3.3<br>4.4 0<br>4.3.1<br>4.3.2<br>4.3.3<br>4.4 0<br>4.3.1<br>4.5.1<br>4.5.1<br>4.5.1<br>4.5.2<br>4.5.3<br>4.6.2<br>4.6.3<br>4.6.4<br>4.7 N<br>4.8 N | 3.2.10   Mixed-Criticality Systems |

|   | 4.9            | Syst   | em Partitioning in MultiPartes                                     | 35 |

|---|----------------|--------|--------------------------------------------------------------------|----|

|   | 4.9.           | 1      | System Partitioning Algorithm and Scheduling                       | 35 |

|   | 4.9.2<br>4.9.3 |        | Input to the Partitioning Algorithm                                | 36 |

|   |                |        | Output of the Partitioning Algorithm                               | 36 |

|   | 4.9.           | 4      | Partitioning Algorithm                                             | 36 |

|   | 4.10           | Chal   | lenges/Shortcomings w.r.t. MCS                                     | 37 |

|   | 4.11           | Refe   | rences                                                             | 37 |

| 5 | Tim            | ing A  | nalysis Algorithms                                                 | 41 |

|   | 5.1            | Ove    | rview                                                              | 41 |

|   | 5.2            | Clas   | sical Approach for Timing Analysis                                 | 41 |

|   | 5.2.           | 1      | Monoprocessor                                                      | 41 |

|   | 5.2.           | 2      | Multiprocessor                                                     | 42 |

|   | 5.3            | Part   | itioned System Scheduling Analysis                                 | 42 |

|   | 5.3.           | 1      | Server-based Scheduling Analysis                                   | 43 |

|   | 5.3.           | 2      | Compositional Scheduling Analysis                                  | 43 |

|   | 5.3.           | 3      | Flat Model Schedulability Analysis                                 | 44 |

|   | 5.4            | Task   | Timing Analysis                                                    | 44 |

|   | 5.5            | Mes    | sage Timing Analysis                                               | 45 |

|   | 5.6            | End    | to-End Timing Analysis                                             | 45 |

|   | 5.7            | Мос    | le Change                                                          | 45 |

|   | 5.8            | Tem    | poral Interference in Multicore Systems                            | 45 |

|   | 5.8.           | 1      | Sources of Indeterminism                                           | 45 |

|   | 5.8.           | 2      | Modeling and Analysis                                              | 46 |

|   | 5.9            | Cha    | lenges/Shortcomings w.r.t. DREAMS                                  | 47 |

|   | 5.10           | Refe   | rences                                                             | 47 |

| 6 | Rea            | l-Tim  | e Faults and Recovery Strategies                                   | 49 |

|   | 6.1            | Intro  | oduction                                                           | 49 |

|   | 6.2            | Faul   | t model                                                            | 50 |

|   | 6.2.           | 1      | Hardware Failures on the Multi-core                                | 50 |

|   | 6.2.           | 2      | Temporal Faults                                                    | 51 |

|   | 6.2.           | 3      | Fault Model for the DREAMS Project                                 | 51 |

|   | 6.3            | Faul   | t-tolerant Strategy                                                | 51 |

|   | 6.3.           | 1      | Recovery Strategy for the Fault Model: Transient Fault             | 53 |

|   | 6.3.           | 2      | Recovery Strategy for the Fault Model: Core is Halted              | 55 |

|   | 6.3.           | 3      | Recovery Strategy for the Fault Model: Temporal Overload Situation | 60 |

|   | 6.4            | Cha    | lenges/Shortcomings w.r.t. MCS                                     | 63 |

|   | 6.5            | Refe   | rences                                                             | 63 |

| 7 | Sche           | edulir | ng Problem Formalization                                           | 67 |

|   |                |        |                                                                    |    |

|    | 7.1   | Gen    | eral problem formulation                                                              | 67  |

|----|-------|--------|---------------------------------------------------------------------------------------|-----|

|    | 7.1.1 |        | Formalization taking into account only timing constraints                             | 68  |

|    | 7.1.2 |        | Formalization taking into account the two levels scheduling – IMA and intra-partit 69 | ion |

|    | 7.1.3 | 3      | Formalization taking into account an execution model                                  | 69  |

|    | 7.2   | Cha    | llenges/Shortcomings w.r.t. MCS                                                       | 70  |

|    | 7.3   | Refe   | erences                                                                               | 70  |

| 8  | Map   | ping   | Algorithms                                                                            | 72  |

|    | 8.1   | ESA    | MA                                                                                    | 72  |

|    | 8.2   | MIL    | P-TECS13                                                                              | 72  |

|    | 8.3   | Cha    | llenges/Shortcomings w.r.t. MCS                                                       | 72  |

|    | 8.4   | Refe   | erences                                                                               | 72  |

| 9  | Offli | ne S   | cheduling Algorithms for DHRTS                                                        | 73  |

|    | 9.1   | Mot    | tivation                                                                              | 73  |

|    | 9.2   | Offl   | ine Scheduling Table Construction                                                     | 73  |

|    | 9.2.3 | 1      | Branch and Bound Based Search                                                         | 74  |

|    | 9.2.2 | 2      | Clustering Algorithm based Search                                                     | 76  |

|    | 9.2.3 | 3      | Clustering + Branch and Bound based Search                                            | 77  |

|    | 9.2.4 | 4      | Genetic Algorithm based Search                                                        | 78  |

|    | 9.2.  | 5      | List Scheduling based Search                                                          | 78  |

|    | 9.2.0 | 6      | Simulated Annealing based Search                                                      | 79  |

|    | 9.2.  | 7      | Other Heuristics based Search                                                         | 80  |

|    | 9.2.8 | 8      | Handling Periodic Tasks with Deadlines greater than Periods                           | 81  |

|    | 9.3   | Offl   | ine Scheduling Table Construction with Flexibility                                    | 82  |

|    | 9.3.3 | 1      | Slot Shifting: Handling Aperiodic Tasks                                               | 82  |

|    | 9.3.2 | 2      | Handling Aperiodic and Sporadic Tasks                                                 | 83  |

|    | 9.3.3 | 3      | Mode Change Algorithm                                                                 | 84  |

|    | 9.3.4 | 4      | TT Scheduling of Mixed Criticality Systems                                            | 84  |

|    | 9.3.  | 5      | Mixed Criticality and TT Legacy Systems                                               | 85  |

|    | 9.3.0 | 6      | Mixed Criticality and TT Scheduling Table Construction                                | 86  |

|    | 9.4   | Cha    | llenges/Shortcomings w.r.t. MCS                                                       | 86  |

|    | 9.4.3 | 1      | Requirements Related to Scheduling in DREAMS                                          | 86  |

|    | 9.4.2 | 2      | Shortcomings of the Current Solutions                                                 | 86  |

|    | 9.4.3 | 3      | Challenges                                                                            | 87  |

|    | 9.5   | Refe   | erences                                                                               | 87  |

| 1( | ) 0   | ffline | e and Incremental Network Scheduling                                                  | 90  |

|    | 10.1  | Net    | work Message Scheduling                                                               | 90  |

|    | 10.2  | Mes    | ssage Scheduling Constraints                                                          | 91  |

| 10.2 | 2.1   | Generic Constraints                                     | 91 |

|------|-------|---------------------------------------------------------|----|

| 10.2 | 2.2   | Incremental Scheduling Constraints                      | 91 |

| 10.3 | Mes   | ssage Scheduling Strategies                             | 92 |

| 10.4 | Net   | work Scheduling for TTEthernet                          | 92 |

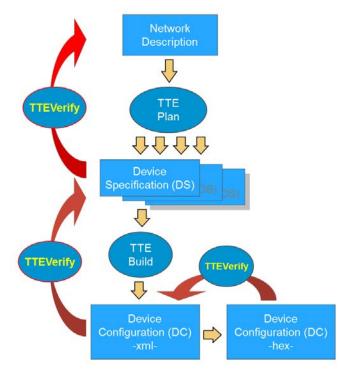

| 10.4 | 4.1   | The TTE-Toolchain                                       | 93 |

| 10.4 | 4.2   | Constraints to TTE-Plan                                 | 93 |

| 10.5 | Cha   | llenges/Shortcomings w.r.t. MCS                         | 94 |

| 10.6 | Refe  | erences                                                 | 95 |

| 11 C | Optim | ization Techniques for Architectural Exploration        | 95 |

| 11.1 | MO    | EA-based Architectural Exploration                      | 95 |

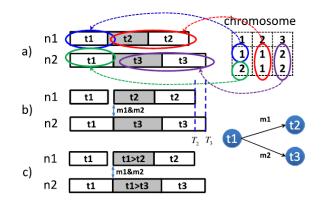

| 11.3 | 1.1   | Optimization Procedure                                  | 96 |

| 11.3 | 1.2   | Schedule Reconstruction                                 | 97 |

| 11.3 | 1.3   | Objective Specification                                 |    |

| 11.3 | 1.4   | Fitness Evaluation                                      |    |

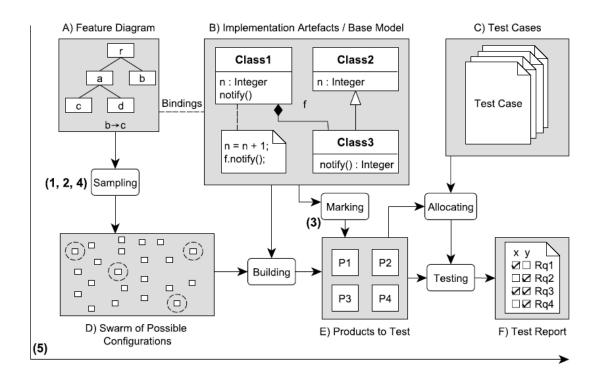

| 11.2 | Prod  | duct-line Testing Technology                            |    |

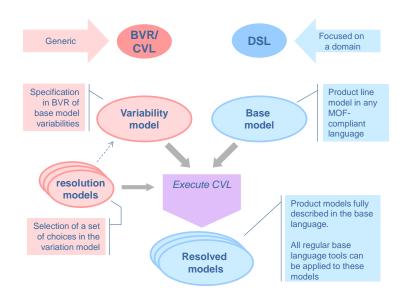

| 11.2 | 2.1   | Modelling Product Lines with BVR (CVL)                  |    |

| 11.2 | 2.2   | Testing Software Product Lines                          |    |

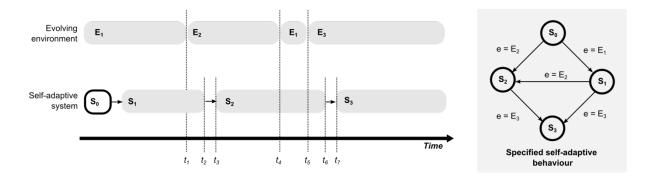

| 11.2 | 2.3   | Product Line Engineering to Build Self-Adaptive Systems |    |

| 11.3 | Cha   | llenges/Shortcomings w.r.t. MCS                         |    |

| 11.4 | Refe  | erences                                                 |    |

# List of Abbreviations

| ASIL    | Automotive Safety Integrity Level                           |

|---------|-------------------------------------------------------------|

| AFDX    | Avionics Full DupleX switched ethernet                      |

| ARP     | Aerospace Recommended Practice                              |

| ASAAC   | Allied Standard Avionics Architecture Council               |

| BTA     | Binary Tree Analysis                                        |

| CFG     | Control Flow Graph                                          |

| CMF     | Common-Model-Failures                                       |

| CMS     | Centralized Maintenance System                              |

| COM/MON | COMmand/MONitoring                                          |

| COTS    | Commercial Off-The-Shelf                                    |

| CPU     | Central Processing Unit                                     |

| CSMA/CA | Carrier Sense Multiple Access with Collision Avoidance      |

| CSP     | Constraint Satisfaction Problem                             |

| DAG     | Directed Acyclic Graph                                      |

| DAL     | Design Assurance Level                                      |

| DDR     | Double Data Rate (Synchronous Dynamic Random Access Memory) |

| DHRTS   | Distributed Hard Real-Time Systems                          |

| DM      | Deadline Monotonic                                          |

| DSE     | Design Space Exploration                                    |

| DUF     | Detectable Unrecoverable Faults                             |

| EA      | Evolutionary Algorithm                                      |

| ECFG    | Extended Control Flow Graph                                 |

| EDF     | Earliest Deadline First                                     |

| FDIR    | Failure Detection Isolation and Recovery                    |

| FIT     | Failure-In-Time                                             |

| FMS     | Flight Management System                                    |

| FPPS    | Fixed Priority Pre-emptive Scheduling                       |

| HAZ     | Hazardous                                                   |

| IEC     | International Electrotechnical Commission                   |

| IMA     | Integrated Modular Avionics                                 |

| LCM     | Least Common Multiple                                       |

| MAJ     | MAJor                                                       |

| MARS    | MAintainable Real-Time System                               |

| MC    | Mixed-Criticality                                               |

|-------|-----------------------------------------------------------------|

| MCS   | Mixed-Criticality System                                        |

| MOEA  | Multi-Objective Evolutionary Algorithm                          |

| MPT   | MultiPARTES (EU funded Project)                                 |

| MTTF  | Maitir Arres (20 funded Project)<br>Mean Time To Failure        |

| NI    | Network Interface                                               |

| NoC   |                                                                 |

|       | Network-On-Chip                                                 |

| PN    | Processing Node                                                 |

| RAM   | Random Access Memory                                            |

| RAMSS | Reliability, Availability, Maintainability, Safety and Security |

| RM    | Rate Monotonic                                                  |

| RWCET | Remaining Worst Case Execution Time                             |

| SDC   | Silent Data Corruption                                          |

| SER   | Soft Error Rate                                                 |

| SEU   | Single Event Upset                                              |

| SIL   | Security Integrity Level                                        |

| SPEA  | Strength Pareto Evolutionary Algorithm                          |

| SWAT  | SoftWare Anomaly Treatment                                      |

| TBFD  | Trace Based Fault Diagnosis                                     |

| TDMA  | Time Division Multiple Access                                   |

| TLTL  | Timed Linear Temporal Logic                                     |

| TMR   | Triple-Modular Redundancy                                       |

| TSP   | Time-Space Partitioning                                         |

| тт    | Time-Triggered                                                  |

| TTE   | Time-Triggered Ethernet                                         |

| ттр   | Time-Triggered Protocol                                         |

| TT-FS | Time-Triggered scheduling with Flexible Slack                   |

| TT-SP | Time-Triggered with Static Priority                             |

| VL    | Virtual Link                                                    |

| WCET  | Worst Case Execution Time                                       |

|       |                                                                 |

### **1** Introduction

This document is the deliverable D4.1.1 - Initial collection of offline adaptation strategies for mixedcriticality of the DREAMS project. It is the first deliverable of task T4.1 - Offline adaptation strategies in mixed criticality, and also of work package WP4 - Architecture, tooling, scheduling and analysis. This deliverable presents an initial collection of offline adaptation strategies. This acts as a starting point for consideration of possible choices of offline schedulers for mixed criticality systems in DREAMS. It also provides definition of certain ambiguous terms related to scheduling to establish a common notion amongst the partners. Since, this is the first deliverable from WP4, it also provides an overview of the model-driven development (MDD) process in DREAMS. The preparation process for this deliverable involved collection of the algorithms/approaches found in the literature and related building blocks provided in DREAMS deliverable D1.1.1 – Architecture conceptualization: requirements, terms and principles, guided by the objectives and partner roles mentioned in the description of work for T4.1 related to the offline adaptation strategies.

### **1.1 Objectives of this Deliverable**

The objective of this deliverable is *"to document an initial set of collected adaptation strategies which forms the basis for the offline configurations for mixed-criticality applications"*. The collected offline adaptation strategies then act as candidates to be considered for selection in the next phase of T4.1 (D4.1.2), that relates to initial implementation of chosen candidates for scheduling of mixed criticality systems in DREAMS.

### **1.2** Positioning of the Deliverable in the Project

The goal of work package *WP4 - Tools, scheduling and analysis* is to define and implement algorithms for the transformation steps of the model driven development process defined by the DREAMS project. To achieve this goal, the work package WP4 is divided in four tasks: T4.1, T4.2, T4.3, and T4.1.

- Task *T4.1 Offline adaptation strategies in mixed criticality* aims at generating offline configurations for mixed-criticality applications satisfying specified global constraints. This is achieved by deriving platform specific model from generic application model and platform model.

- Task *T4.2 Generation of platform configuration files* aims at automatic generation of hardware and software configuration files out of a platform-specific model (computed by Task T4.1) instead of error-prone human translation.

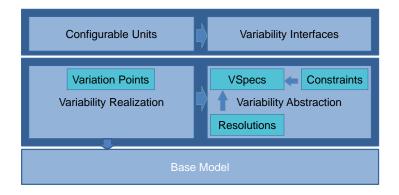

- Task *T4.3 Explicit variability configuration* aims at specification of the variability for the generic application model and platform model (obtained from task T1.4) and binding the variability with generic application model and platform model. These generic models with bounded variability then serve as input to the task T4.1.

- Task *T4.4 Tool integration and demonstrator support* aims at promoting and supporting the usage of WP4 results in WP6 avionics demonstrator, WP7 wind power demonstrator and WP8 healthcare demonstrator.

Task T4.1, in order to achieve it's aim, needs the following input from other tasks in the project:

- The generic application model and platform model from task T1.4 Development of methods for application, platform and variability modelling of WP1 Architecture,

- Variability extensions from task T4.3 of WP4,

- Local resource management schemes and strategies from T2.2 Resource management and adaptation services for mixed criticality and T2.3 System software extensions for SoC virtualization of WP2 Multicore virtualization technology, network scheduling and

- Global resource management services from T3.2 Cluster-level safety and security of WP3 Mixed-criticality network, and

- The power models from T1.4 of WP1.

On the other hand, the output (offline configurations) generated by the task T4.1 (in D4.1.2 and D4.1.3) is needed as input by the following tasks:

- Task *T2.1 Virtualization and memory interleaving extensions at network interface* of *WP2* to (a) limit contention of time-triggered packets in inter and intra-clusters, and (b) prevent inconsistent configurations.

- Task T2.2 of WP2 needs the strategies and algorithm for mixed criticality and the parameters used at runtime to decide the switching between configurations determined in task T4.1

- Task *T3.3 Global resource management* of WP3 needs the pre-computed configurations from task T4.1 to reconfigure the system at the global level, when needed.

Since, this deliverable relates to task T4.1, we list below the deliverables of task T4.1 that will be provided during the course of the project and highlight the relations between them:

1. *D4.1.1 - Initial collection of offline adaptation strategies for mixed-criticality* (due in July 2014 – this deliverable)

The collected offline adaptation strategies in this deliverable will act as possible candidates for extension, to solve the scheduling problem related to mixed criticality systems in DREAMS, in the next phase of T4.1 i.e. deliverable D4.1.2.

- D4.1.2 Definition of offline adaptation strategies for mixed criticality and initial implementation (due in March 2015) In D4.1.2, based on the collected offline adaptation strategies in deliverable D4.1.1, criteria would be determined for selection of appropriate candidates. Based, on the criteria, the selected approaches will then be considered for scheduling in mixed-criticality systems as envisioned in the project.

- D4.1.3 Final Implementation and improvement of the offline adaptation strategies for mixed criticality (due in July 2016)

Based on the selected candidates in D4.1.2, D4.1.3 will provide final model implementation towards scheduling of mixed-criticality systems.

The dissemination level of this deliverable is public (PU) i.e. once approved by the European Commission (EC), it will be freely available for download through the DREAMS project website (<u>http://dreams-project.eu</u>).

### **1.3 Organization of the Deliverable**

The deliverable is structured into two parts. Part A presents the general notions related to scheduling and comprises of chapters 2, 3, 4, 5, and 6. Part B presents approaches to generate schedules for time-triggered systems and comprises of the rest of the chapters from 7 to 11.

In part A,

• Chapter 2 presents the overview of model-driven development (MDD) process in DREAMS. This is relevant as task T4.1 relates to the mapping and scheduling in the MDD process.

- Chapter 3 establishes a common notion of the scheduling related terms that could be used ambiguously.

- Chapter 4 provides an overview of the classical scheduling approaches using servers, partition scheduling algorithms, approaches for static schedule generation and global and partitioned multiprocessor scheduling.

- Chapter 5 presents techniques for task timing analysis, message timing analysis, end-to-end timing analysis and partitioned systems scheduling analysis.

- Chapter 6 provides a background of the two faults hardware faults and temporal faults, and then presents different fault recovery strategies.

In part B,

- Chapter 7 formalizes the scheduling problem considering timing constraints, two-level (IMA-level and intra-partition scheduling), and different execution models.

- Chapter 8 briefly shows two recent mapping algorithms.

- Chapter 9 presents initial solutions available for scheduling of mixed criticality applications in distributed hard real-time systems and various approaches for offline scheduling table generation for distributed hard-real-time systems.

- Chapter 10 provides an overview of different message scheduling strategies and constraints.

- Chapter 11 describes the multi-objective evolutionary algorithms (MOEA) based architectural exploration. It also provides an overview of the product-line testing technology.

Each chapter (from chapter 3) also has a dedicated section on challenges/shortcomings of the presented approaches w.r.t. the scheduling in DREAMS for mixed-criticality systems, which is relevant for the next phase of T4.1 i.e. deliverable D4.1.2.

### 2 Overview of the Model Driven Development Process

### 2.1 Introduction

The purpose of this section is to summarize the DREAMS development process with a focus on the platform configuration activities performed in the specification and implementation branch of the development process. In following, the suggested model-driven approach and its relation to the offline adaptation strategies collected in this deliverable will be discussed. More details on the development process and the corresponding tool support will be presented in the following deliverables:

- D1.3.1 "Description of development process with model transformations"

- D4.4.1 "Tools feature map and interoperability capabilities"

Furthermore, certification aspects in the development process and the tool-chain will be addressed in D5.4.1 "Guidelines for process and tool integration".

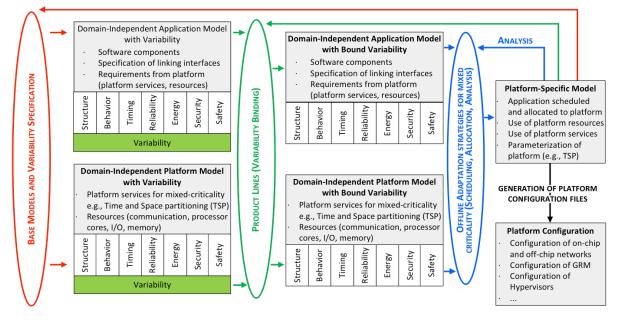

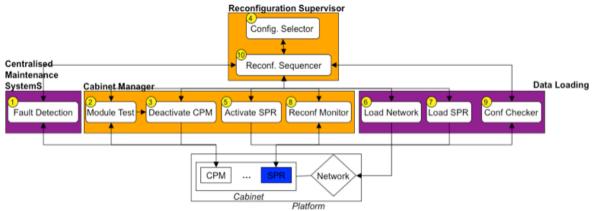

Figure 2-1 Proposed DREAMS Model Driven Development Process

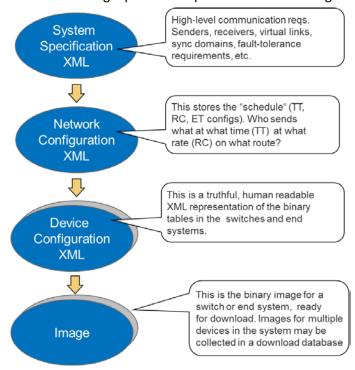

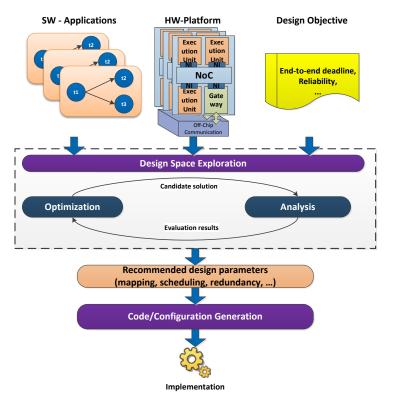

The development process is structured into a processing chain (colored ovals in Figure 2-1, from left to right) which operates on models that provide different views onto the system under design. Here, each of the steps defines an entry point to the development process that starts at a different level of abstraction.

In the following, the basic workflow that is required to put a DREAMS system into operation will be summarized:

• In the DREAMS model driven development process, offline adaptation strategies for mixed criticality systems, (blue oval) serve as the entry point to the development process. The applied methods are used to compute a deployment of an application to an instance of the DREAMS platform. This step uses models of the application subsystems and a platform model as input. The result of this process is a platform-specific model that contains information about the deployed application. In the figure, the blue backward arrow ("analysis") indicates that this step is an optimization process where different deployment alternatives are explored and that it provides analysis methods to rate the eligibility or

quality of a particular solution. The required algorithms and tools for this step are developed in T4.1.

• In the next step (bottom right in the figure), the platform-specific model is used as input for the backend of the processing chain that *generates configuration files* for the different HW/SW components of the target platform. T4.2 covers this part of the workflow.

Based on the above basic workflow that handles the configuration of a single system, the following extended development process can be defined which considers entire product-line families.

- In this case, the process starts with the definition of *base models and variability specification* (red oval in Figure 2-1). Here, a system model consisting of an application model and a platform model (see above) are used as base models. Additionally, the system designer provides a (separate) variability specification that defines which parts of the base model can be varied. Hence, the base model serves as template which is augmented with appropriate variation points. This step in the workflow is covered by task T4.3.

- Together, both models span an entire product-line family from which particular members can be selected. In the figure, this selection step is designated as variability binding (green oval), since for all variation points, a concrete choice is made. Task T4.3 also covers this step in the workflow. The result of this process is a system model that can be further processed using the basic workflow pointed out above.

- The green and red backward arrows in the figure indicate that also in this workflow, the eligibility and quality of the deployed system is rated. In case the selected solution does not satisfy all requirements, the following two options exist: At first, a different variability binding is selected (indicated by the green backward arrow), i.e. a different member of the product-line family is used as input for the basic workflow. In case the last step was not successful, the designer changes the definition of the product-line by modifying the base model and/or the variability specification (red arrow).

### 2.2 Models

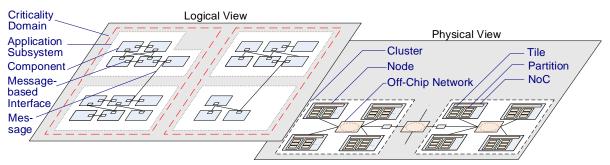

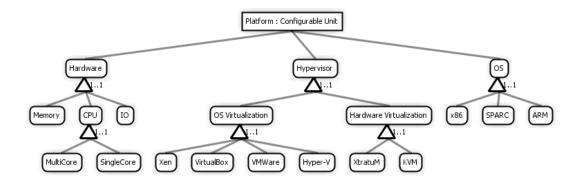

The system model introduced in D1.2.1 summarizes the information to be provided by the DREAMS meta-models<sup>1</sup>. In Figure 2-2, the structure of a DREAMS system is sketched such way that is divided into a logical view (of the application) and a physical view (of the platform).

Figure 2-2 System Structure of Application (Logical View) and Structure of Platform (Physical View) [D1.2.1]

The purpose of the logical view is to provide the following information about mixed-criticality applications in a platform-independent way:

<sup>&</sup>lt;sup>1</sup> The meta-models will be defined in D1.4.1 and D1.6.1. A preview of meta-models and model-transformations as well as an overview of existing building blocks will be presented in D1.3.1.

- Criticality-levels: A system is structured into criticality levels from the different application domains (e.g., DAL A to E in avionics, SIL 1-4 in multiple domains according to IEC-61508 and ASIL A to D in automotive out-of-scope for DREAMS demonstrators).

- Component service: The specification of a component's interface defines its services, which are the intended observable behaviour as perceived by the transmission of messages as a response to inputs, state and the progression of time. Three types of messages are distinguished based on their timing, namely *periodic messages, sporadic messages,* and *aperiodic messages*.

The physical view of a DREAMS system defines the following hierarchical structure:

- The overall system is physically structured into a set of *clusters*.

- Each cluster consists of *nodes*.

- Each node is a multi-core chip containing *tiles*.

- A tile can be processor cluster with several processor *cores*, caches, local memories and I/O resources. Alternatively, a tile can also be a single processor core or an IP core.

- The processor cores within a tile can run a *hypervisor* that establishes time-and-space partitions, each of which executes a corresponding software component.

The communication between the above entities is provided by the following components:

- The connection between clusters is provided by *inter-cluster gateways* that are formed by *off-chip gateways* located between two clusters.

- Nodes are interconnected by an *off-chip real-time communication network*.

- Tiles are interconnected by a *Network-on-Chip* (NoC). Each tile provides a Network Interface (NI) to the NoC offering ports for the transmission or reception of NoC messages.

- An *on/off-chip gateway* is responsible for the redirection of messages between the NoC and the off-chip communication network.

- Off-chip and on-chip networks are responsible ensuring for time and space partitioning as well as the integrity of messages between the respective communication partners.

In order to provide their specified services, components of the logical view must be mapped to the resources of the physical platform:

- Components must be assigned to partitions with suitable computational resources

- Messages must be mapped to the communication networks, taking into account the required timing and reliability properties, and the routing between different parts of the physical platform.

### **3** Terminology/Definitions

In section 3.1, we provide a common notion of 14 terms related to scheduling to remove ambiguity amongst partners in Task T4.1 in DREAMS . In section 3.2, we again list the terms and their definitions related to scheduling from the terminology provided in the deliverable D1.1.1 in DREAMS.

### **3.1 Newly Defined Terms**

### 3.1.1 Aperiodic Task

It is a sequence of jobs or single jobs with variable inter-arrival time or unknown arrival time.

### 3.1.2 Application-specific Constraints

Constraint used to enforce or prevent the mapping of tasks to specific processing elements in order to satisfy application-specific requirements. For instance, a task that requires access to I/O signals must be mapped to that processor core that can access the corresponding peripheral.

### 3.1.3 End-to End Flow (ETEF)

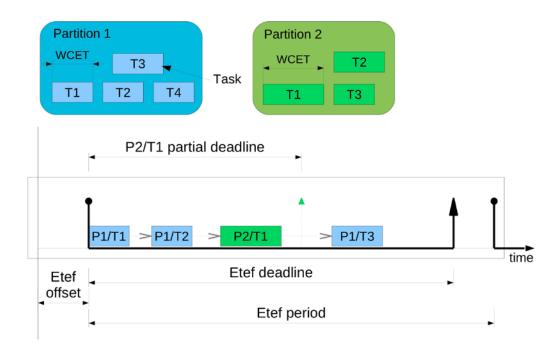

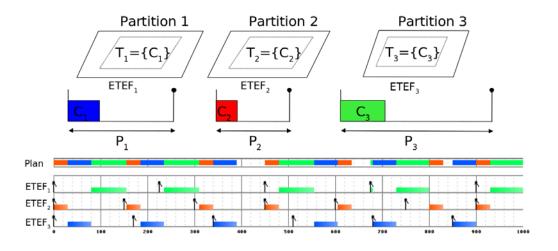

A sequence (sorted list) of one or more execution units (tasks, threads, or processes) and associated timing constraints (period, deadline, offset, etc.)

### 3.1.4 End-to-End Latency

An end-to-end latency is the maximal time required to execute a functional chain, where a functional chain describes the behavior of a sequence of functions, not necessarily hosted on a shared core (or multi-core), from an input until the production of an output.

### 3.1.5 Fault Model

A fault model describes the types of failures that could encounter a system. "A fault model is nothing more than a statement of how the system is expected to fail." [Koo96]

### 3.1.6 Mapping

Mapping simply refers to the assignment of tasks (frames or messages) to processors (virtual links).

### 3.1.7 Mode

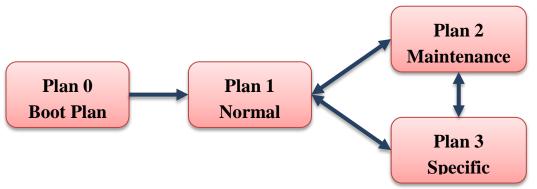

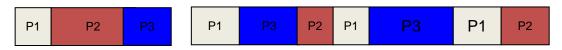

In time-triggered (TT) systems, a mode refers to a phase of operation of a real-time system. For example, an aircraft goes through various phases during its flight: take-off, normal-flight and landing phases. The tasks performed in each of these phases change. So, a mode best captures a particular phase of operation of a real-time system, through a corresponding scheduling table [Foh93].

### 3.1.8 Mode-change

In TT systems, a mode-change refers to the deterministic switching among a number of <u>modes</u> (essentially <u>TT scheduling tables</u>) such that the offline-scheduled real-time system is able to adapt to changing environmental situations. It is a system-wide change [Foh93].

### 3.1.9 Partition Scheduling Plan

In XtratuM, a partition scheduling plan provides information about which <u>partition</u> executes at each point in time based on the global time for each CPU.

### 3.1.10 Partition Slot

A partition slot is the amount of time that a partition can execute without other partition's preemption.

### 3.1.11 Periodic Task

It is an infinite sequence of jobs with constant inter-arrival time (period).

### 3.1.12 Restartable Task

Defined in the WP6. "Asynchronous process associated with a manager process in charge of the activation and cancellation of the computation" (DREAMS D6.1.1)

### 3.1.13 Schedule Reconstruction

Two-step encoding used in MOEA-based architectural exploration that has initially been introduced in [Luk07] in order to minimize the size of the chromosome by only storing the task mapping and the redundancy configuration in it. If the full schedule is required in the fitness evaluation of a candidate solution, a scheduler is used to rebuild the schedule from the information contained in the chromosome.

### 3.1.14 Scheduling

Scheduling deals with the allocation of resources in time to tasks such that the specified constraints like temporal, communication, synchronization constraints etc. are met.

### **3.1.15 TT Scheduling Table**

A TT-scheduling table provides information about which task needs to be assigned the TT slot based on the global time. A TT scheduling table represents a feasible schedule. At runtime, the dispatcher simply executes the decisions in the TT scheduling table.

### 3.1.16 Single Event Upset (SEU)

A single event upset (SEU) is a change of state caused by electromagnetic rays. The effect of such particles on multi-core platform is the switch of a bit memory (in the DDR, local buffers in the internal bus, the caches or the processor registers).

### 3.1.17 Sporadic Task

It is an infinite sequence of jobs with a minimum inter-arrival time.

### 3.1.18 Task

A task is a piece of code executing sequentially on the CPU.

### 3.1.19 TT Slot

In TT systems, the time axis is statically partitioned into slots referred as TT slots. All TT slots have the same fixed-length [Kop11].

### 3.2 Terms Defined in D1.1.1 - Architecture Conceptualization: Requirements, Terms and Principles

### 3.2.1 Assurance Level

The assurance level is determined from the safety assessment process and hazard analysis by examining the effects of a failure condition in the system.

For example, DO-178B distinguishes five assurance levels in avionics: Level A (Catastrophic) refers to systems where a failure that may cause a crash, Level B (Hazardous) implies a large negative impact on safety), Level B (Major) involves a significant, but lesser impact than a hazardous failure, Level C (Minor) refers to an even lesser impact on safety. The failure of a Level E system has no safety effect. [DREAMS D1.1.1]

### 3.2.2 Error

An error is that part of the system state which is liable to lead to a subsequent failure. A <u>failure</u> occurs when the error reaches the service interface. [DREAMS D1.1.1]

### 3.2.3 Failure

A failure occurs when the delivered service deviates from fulfilling its specification. [DREAMS D1.1.1]

### 3.2.4 Fail-operational System

A fail-operational system is able to tolerate one or several <u>faults</u>. Fail-operational systems send correct messages despite the failure of their subsystems. [DREAMS D1.1.1]

### 3.2.5 Fail-safe system

If a fail-safe system one or more safe states can be reached in case of a system <u>failure</u>. Fail-safeness is a characteristic of the controlled object, not the computer system. In fail-safe systems the computer system must have a high error-detection coverage. [DREAMS D1.1.1]

### 3.2.6 Fault

A fault is the adjudged or hypothesized cause of an <u>error</u>. Faults can be internal or external of a system.

Examples of types: An external fault (e.g. a malicious attack) causes an error, and possible a subsequent <u>failure</u>. An internal fault (i.e. vulnerability) allows an external fault to harm the system and has to pre-exist in the system. [DREAMS D1.1.1]

### 3.2.7 Fault-Containment Region

A Fault Containment Region (FCR) is a subsystem that operates correctly regardless of any arbitrary logical or electrical <u>fault</u> outside the region. [DREAMS D1.1.1]

### 3.2.8 Fault Hypothesis

The fault hypothesis is the specification of the <u>faults</u> that must be tolerated without any impact on the essential system services. The fault hypothesis states the assumptions about units of failure (see <u>Fault Containment Region</u>), failure modes, failure frequencies, failure detection, and state recovery. [DREAMS D1.1.1]

### 3.2.9 Latency Constraint

A latency constraint describes how occurrences of a "target" event are placed relative to each occurrence of a "source" event. Source and target events are specified by a timing event chain.

Every instance of the source event must be matched by an instance of the target event, within a time window starting at lower and ending at upper time units relative to the source occurrence. [DREAMS D1.1.1]

### 3.2.10 Mixed-Criticality Systems

Mixed-criticality is the concept of allowing application subsystems that must meet different <u>assurance levels</u> (e.g., ranging from DAL A to DAL E in RTCA DO-178B, SIL1 to SIL4 in EN ISO/IEC 61508) to seamlessly interact and co-exist on the same networked distributed computational platform. [DREAMS D1.1.1]

### 3.2.11 Partition

A partition is the execution environment for a component with corresponding resources (e.g., processor, memory, communication, input/output). The resources for a partition are protected by temporal partitioning and <u>spatial partitioning</u> in order to avoid unintended feature interaction and fault propagation between components. [DREAMS D1.1.1]

### 3.2.12 Repetition Constraint

A Repetition constraint describes the distribution of the occurrences of a single event. Typical examples of these events are Task Activation, Frame Instantiation, Task Execution End, Frame Transmission End.

Prominent examples of repetition constraints are periodic repetition with jitter and sporadic repetition with minimal inter-occurrence time. [DREAMS D1.1.1]

### 3.2.13 Spatial Partitioning

Spatial partitioning ensures that the service in one <u>partition</u> cannot alter the code or private data of another partition. Spatial partitioning shall also prevent a partition from interfering with control of external devices (e.g., actuators) of other partitions. [DREAMS D1.1.1]

### **3.2.14 Synchronization Constraint**

A Synchronization constraint describes how tightly the occurrences of a group of events follow each other. This is typically expressed by a temporal window, i.e. an upper bound on the temporal distance between the occurrences of the events of the group.

An example is the reading of input data from different sensors, which must occur in a small time window to ensure a temporally consistent view of the environment. [DREAMS D1.1.1]

### **3.2.15 Temporal Partitioning**

Temporal partitioning ensures that a <u>partition</u> cannot affect the ability of other partitions access shared resources, such as the network or a shared CPU. This includes the temporal behavior of the services provided by resources (latency, jitter, duration of availability during a scheduled access). [DREAMS D1.1.1]

### 3.2.16 Timing Constraint

A Timing Constraint is a constraint on the occurrence times of one or more Timing Events. [DREAMS D1.1.1]

### 3.2.17 Worst Case Execution Time (WCET)

The Worst Case Execution Time is the maximal delay needed to execute all instructions of a task, excluding interruption or preemption delays. [DREAMS D1.1.1]

### 3.2.18 Worst Case Response Time (WCRT)

The Worst Case Response Time is the worst delay between the occurrence time of the Task Activation and the occurrence time of the Task Execution End. With respect to the WCET, it includes interruption/preemption or initial blocking delays (non-preemptive scheduling). [DREAMS D1.1.1]

### 3.3 References

[Foh93] G. Fohler, "Changing Operational Modes in the Context of Pre Run-Time Scheduling," *IEICE Transactions on Information and Systems*, vol. Special Issue on Responsive Computer System, 1993.

[Luk07] M. Lukasiewycz, M. Glaß, C. Haubelt, and J. Teich. (2007). SAT-decoding in evolutionary algorithms for discrete constrained optimization problems. In *Proceedings of the IEEE Congress on Evolutionary Computation (CEC 07)*, pages 935–942.

[DREAMS D1.1.1] C. DREAMS, "D1.1.1 - Architecture Conceptualization: Requirements, Terms and Principles," DREAMS Consortium 2014.

[Koo96] Philip J. Koopman, "Lost Messages and System Failures". Embedded Systems Programming, 9(11), October 1996, pp. 38-52.

[Kop11] H. Kopetz, *Real-Time Systems: Design Principles for Distributed Embedded Applications*, Second Edition ed.: Springer-Verlag New York Inc, 2011.

### 4 Hierarchical Scheduling Algorithms

### 4.1 Overview

In the last years, embedded systems have increased its processing capabilities and its computational resources in such a way that they are capable of executing several concurrent real-time applications that would formerly have required to be implemented on separate hardware platforms. Allocating several applications to a single processor not only reduces cost, but also ensures better reliability, as the overall complexity of the system is reduced.

CPU-sharing is implemented by some kind of partitioning scheme that time-multiplexes the physical resources among the different application task groups, with the goal that each application task group may be programmed as if it had dedicated access to a physical resource, i.e., without interference from other task groups due to resource sharing. When composing a system comprising a number of applications, it is typically a requirement to provide temporal isolation between the various applications. Temporal isolation means that the processor time budget available for an application is guaranteed in spite of other applications possibly overrunning their budgets.

There is currently considerable interest in hierarchical scheduling as a way of implementing partitioned systems.

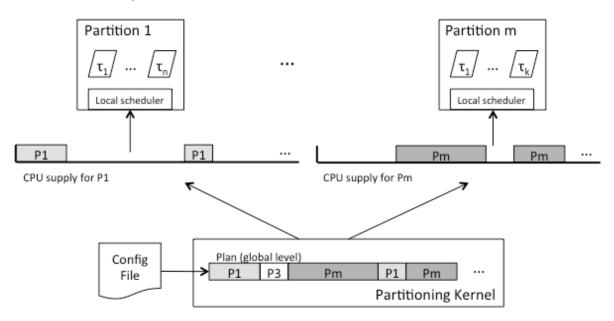

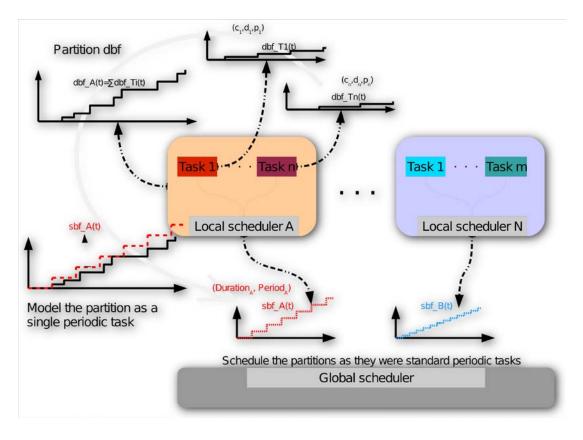

### 4.2 Hierarchical Scheduling in Partitioned Systems

In a hierarchical system, a global scheduler is used to determine which application should be allocated the processor at any given time, and a local scheduler is used to determine which of the chosen application's tasks should actually execute. A number of different scheduling schemes have been proposed for both global and local scheduling. These include cyclic or time slicing frameworks, dynamic priority based scheduling and fixed priority scheduling. For example, ARINC653 defines a cyclic scheduler at the global level and a fixed-priority scheduler at the local level [ARINC653].

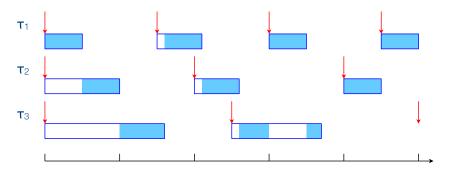

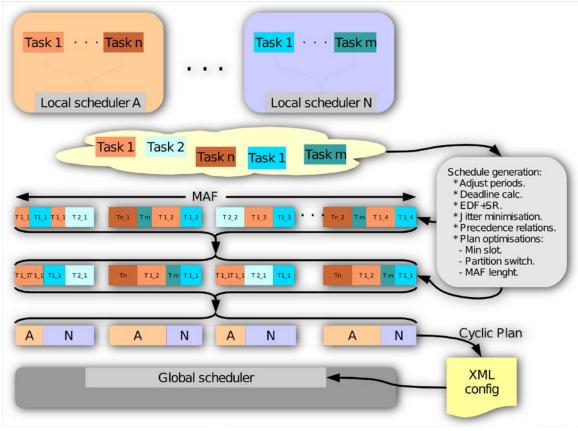

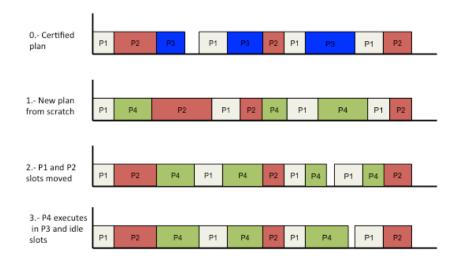

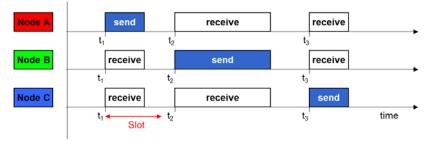

Next Figure shows an example of a partitioned system with a hierarchy of two levels. In the global level, the scheduling is based on a table written in a static configuration file that establishes the temporal windows (or slots) in which partitions will execute. These slots are passed to each local scheduler that manages tasks execution inside these slots.

In the next sections, scheduling algorithms and schedulability analysis will be described for the global (hypervisor) and the local (partition) levels.

### 4.2.1 Hypervisor Scheduling

Traditionally, the scheduling method used in the global level has been static or dynamic.

### 4.2.1.1 Static Scheduling

Under this approach the system is analysed off-line and a static schedule (or table) is generated.. Each row of the table defines a sequence of jobs that are executed on the occurrence of a timer signal, usually an interrupt generated by a hardware timer. Such a sequence is called a *frame* or a *minor cycle*. The whole table defines a global repetitive behaviour for the system, which is called a *major cycle*. The major cycle period is the *hyperperiod* of the system, which is the least common multiple (lcm) of all the task periods:

### $H = \text{Icm } T_{i}$

This method is sometimes used in critical systems as it provides a deterministic real-time behaviour, which can be easily analysed with respect to real-time requirements for verification and validation purposes. It can be implemented with a simple, robust run-time scheduler (commonly called a *cyclic executive*), without the need for a full-fledged operating system kernel. Access to shared data poses no problem as long as critical regions are kept within a single. Schedulability analysis is performed at the time of building the scheduling table, i.e. at design time.

In spite of its simplicity and robustness, static scheduling has some drawbacks that may make it inappropriate for systems with some degree of complexity:

- Static scheduling requires that all tasks are periodic. Sporadic tasks can only be incorporated in the form of *poll servers*, i.e. periodic tasks that check if an event has occurred and execute the associated sporadic job if this is the case.

- The generation of the scheduling table may be quite a complex problem. In the general case it has been proved to be NP-complete, although some heuristics have been proposed that can be used in many practical situations to compute a feasible schedule in polynomial time [Li00][BW09]. In practice, designers often adjust the task periods so that they are harmonic, i.e. multiples of each other.

- Even with harmonic periods, tasks with very long periods are very difficult to accommodate.

- Tasks with long execution times may have to be split into a number of shorter segments in order to find a feasible schedule.

### 4.2.1.2 Dynamic Scheduling

In dynamic scheduling, it is common to use server-based algorithms. Server-based scheduling provides a way to reserve a fraction of processor time. In this approach, a separate server is allocated to each application. Each server has an execution capacity and a replenishment period, enabling the overall processor capacity to be divided up among the different applications. Each server has a unique priority that is used by the global scheduler to determine which of the servers with remaining capacity, and which tasks that are ready to execute, should be allocated the processor. Several kinds of server algorithms have been defined, which differ in the way their budget is replenished, and how they deal with unused budget. The most common ones for fixed-priority are:

• *Periodic server*. A periodic server or *polling server* is a periodic task with period  $T_s$  and budget  $C_s$ . Whenever it is activated, if there is any aperiodic job pending, it is executed as long as there is some budget available. Otherwise, the server suspends itself until the next period. Unused budget cannot be saved for possible future jobs. If an aperiodic job is requested later in the same period, its execution is postponed until the next period.

If the budget is fully consumed, the job execution is suspended until the start of the next period, at which time the budget is replenished.

A periodic server is commonly assigned the highest priority, and its interference on other tasks can be calculated using response-time equations.

• *Deferred server*. A deferred server [LSS87] is similar to a periodic server, but it saves its unused budget until the end of its period. If an aperiodic job is requested at any time within the period, it is immediately dispatched for execution. The budget is replenished at the start of each period, and unused budget from the previous period is lost.

Deferred servers are usually assigned the highest system priority. RTA equations can be adapted to deal with server interference on real-time tasks.

• Sporadic server. A sporadic server [SSL89] is similar to a deferred server, but its budget is replenished using more complicated rules, which enable better processor utilization and faster response times for sporadic jobs. There are several variants of the basic sporadic server algorithm, but in any case the effects of the sporadic server on the timing behaviour of other tasks are not worse than those of an equivalent periodic task.

Sporadic servers can be assigned any priority in the system priority range. In terms of schedulability analysis, a sporadic server is equivalent to a sporadic task and can thus be easily accommodated within RTA.

Although dynamic-priority versions of deferred and sporadic servers that can be used with Earliest Deadline First (EDF) have been defined (see e.g. [Bu10]), there are some kinds of servers that have been developed specifically for EDF.

The best-known dynamic priority servers are [SB94]:

- *Priority exchange server*. A priority exchange server is similar to a deferrable server, but its unused capacity is not lost, but exchanged for the execution time of a lower-priority task, i.e. a task with a longer absolute deadline.

- *IRIS (Idle-Time Reclaiming Improved Server*) ([MSP04]): Based on the Constant Bandwidth Server (CBS, [AB04]), it allows the coexistence of hard, soft and non real-time tasks. The proposed algorithm is specifically designed to handle computational overload. A task that needs more CPU-time than reserved can re-use the spare bandwidth, without interfering with the others tasks. With respect to other reclamation schemes, the novelty of IRIS algorithm is that the spare bandwidth is fairly distributed among the needing servers.

- Total bandwidth server. A total bandwidth server tries to shorten the response time of aperiodic requests (1,..k) by assigning them all the available processor time. More specifically, if a maximum utilization  $U_s$  is assigned to the server at design time, a new aperiodic request with computation time  $C_k$  released at  $r_k$  is assigned an absolute deadline

$$d_k = \max(r_k, d_{k-1}) + \frac{C_k}{U_s}$$

and then it is scheduled using EDF, as any other task.

Overall, it can be said that the total bandwidth server has best performance [Bu10].

### 4.2.2 Partition Scheduling

Most used scheduling algorithms for the local level (internal scheduling of tasks inside a partition) are priority based scheduling algorithms. Most popular priority based algorithms Rate-Monotonic and Deadline Monotonic if the priority is fixed. Earliest Deadline First is the most popular if the priority can change during run time execution. However, ARINC-653 allows a fixed-priority scheduler on the local level.

### 4.2.2.1 Fixed-Priority Assignment