# Towards a European Strategy for Cyber-Physical Systems

Concertation Workshop on Mixed-Criticality Systems and Multicore

Distributed REal-time Architecture for Mixed criticality Systems (DREAMS)

Roman Obermaisser University of Siegen

## **Project General Information**

- Project full title: Distributed REal-time Architecture for Mixed criticality Systems

- Project duration: October 1, 2013 Sept. 30, 2017

- Type of project: Integrated Project (IP)

- Budget Total: 15.5 mill. EUR

- Coordinator: Roman Obermaisser (Univ. of Siegen)

| Industry | Thales SA            | France  |

|----------|----------------------|---------|

|          | Alstom Wind S.L.     | Spain   |

|          | STMicroelectronics   | France  |

|          | TÜV Rheinland        | Germany |

| SME      | TTTech               | Austria |

|          | RealTime-At-Work     | France  |

|          | Virtual Open Systems | France  |

|          | FENTISS              | Spain   |

| Research Org. | ONERA              | France  |

|---------------|--------------------|---------|

|               | Ikerlan            | Spain   |

|               | SINTEF             | Norway  |

|               | Fortiss            | Germany |

| Univ.         | Universität Siegen | Germany |

|               | TU Kaiserslautern  | Germany |

|               | UPV                | Spain   |

|               | TEI                | Greece  |

# **Project Description**

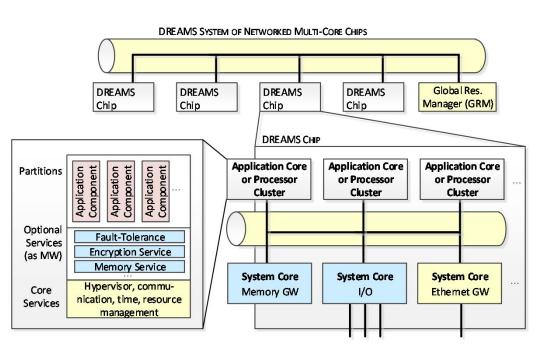

Mixed-criticality architecture based on networked multicore chips

- 1. Architectural style and modelling methods

- 2. Virtualization technologies for security, safety, realtime performance, integrity in networked multi-core chips

- 3. Adaptation strategies for mixed-criticality systems

- Development methodology and tools based on modeldriven engineering

- 5. Certification and mixed-criticality product lines

- Feasibility of DREAMS architecture in real-world scenarios

- 7. Promoting widespread adoption and community building

#### **Main Technical Activities**

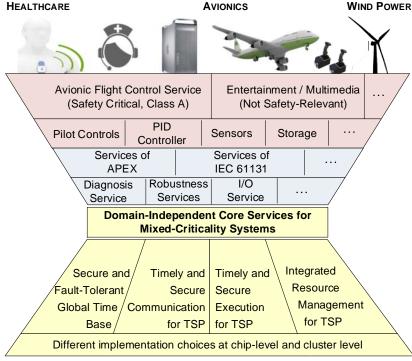

- Cross-domain architectural style and models for MCS

- Modular certification and mixed-criticality product lines

- Platform with virtualization at chip and network level

- Adaptation strategies for mixed-criticality systems

- Development methodology, variability management and tools

### **Main Outcome and Results**

- Reduced development cost and time-to-market for mixedcriticality applications

- Exploitation of economies of scale through cross-domain components and tools

- Consolidation and integration of virtualization solutions and development methods from previous projects

- Significant advances in virtualization techniques leading to higher reliability, security and safety

- Higher flexibility, adaptability and energy efficiency through integrated resource management

- Leverage multi-core platforms for a system perspective of mixed-criticality applications combining the chip-level and network-level

## **Exploitation Plans**

- Exploitation in the industrial application domains (avionic, wind power, and healthcare domains)

- Integrating the DREAMS methodology and the related tools into respective production processes

- Tailoring of DREAMS outcomes to the individual application fields and company approaches

- Cross-domain exploitation and transfer to additional domains (e.g., automotive, railway)

- Exploitation of DREAMS platform and methodology building blocks

- Translation of DREAMS platform and methodology into product-ready implementations

- Examples

- Commercialization of tools and use in R&D studies (e.g., simulation tools, tools for architecture exploration)

- Extension of execution environments for MCS using resource virtualization techniques (e.g., distributed, extensible hardware IOMMU, hardware-enhanced virtualization, ...)

- Contribution to standards, regulations and open source (e.g., SAE, IEEE, ARINC and ISO/IEC)